fxl3sd206 Fairchild Semiconductor, fxl3sd206 Datasheet

fxl3sd206

Available stocks

Related parts for fxl3sd206

fxl3sd206 Summary of contents

Page 1

... For Fairchild’s definition of “green” Eco Status, please visit: http://www.fairchildsemi.com/company/green/rohs_green.html. © 2009 Fairchild Semiconductor Corporation FXL3SD206 • Rev. 1.0.0 Description FXL3SD206 is a voltage translator with multiplexing and de-multiplexing functions for SDIO devices designed for voltage translation over a wide range of DD input and output levels, from 1 ...

Page 2

... Card Select HOST CMD Output Enable CLK D0~D3 Figure 1. Single Host to Two SDIO Application Diagram SD Memory Or CMD SDIO Device CLK D0~D3 © 2009 Fairchild Semiconductor Corporation FXL3SD206 • Rev. 1.0.0 Power Management IC VDD_LO VDD_HI VDD_SEL CH_SEL CMD_B In MUX Out In CMD_ A Out DEMUX In CMD_C OE Out ...

Page 3

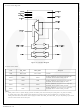

... VDD_LO 19 VDD_HI 20 VDD_CON 21 VDDA 22 VDD_SEL 23 CH_SEL 24 OE © 2009 Fairchild Semiconductor Corporation FXL3SD206 • Rev. 1.0 Figure 3. Pin Configuration (Top Through View) Type Description Data Data Pin of A Port Data Data Pin of A Port Data Data Pin of A Port Data ...

Page 4

... In single host mode, VDD_CON should be tied to the same supply as the VDDA pin. In dual host mode, VDD_CON should be tied to the same supply as either the VDD_HI or the VDD_LO pin, depending upon which host is used to drive the control pins. © 2009 Fairchild Semiconductor Corporation FXL3SD206 • Rev. 1.0.0 Figure 4. Function Diagram VDD_SEL Don’t Care 3-State Normal operation ...

Page 5

... All unused inputs and input/outputs must be held During normal operation The input and output voltages of Ports B and C are determined by which V © 2009 Fairchild Semiconductor Corporation FXL3SD206 • Rev. 1.0.0 Conditions VDDA, VDD_HI, VDD_LO, VDD_CON Data Ports A, B, and C Control Inputs (OE, CH_SEL, VDD_SEL) Output 3-State ...

Page 6

... Don’t Care ON OFF OFF ON ON © 2009 Fairchild Semiconductor Corporation FXL3SD206 • Rev. 1.0.0 may The recommended power-up sequence is Apply the power to the first V 2. Apply the power to the second V 3. Set the CH_SEL and VDD_SEL pin according to below table the application ...

Page 7

... During normal operation, VDD_HI must be greater than or equal to VDD_LO. 7. This is the output voltage for static conditions. Dynamic drive specifications are given in “Dynamic Output Electrical Characteristics. © 2009 Fairchild Semiconductor Corporation FXL3SD206 • Rev. 1.0.0 Condition Data Inputs Dn_A, CMD_A, CLK_A, Data Inputs Dn_BC, CMD_B, CLK_BC, CH_SEL=H ...

Page 8

... An external driver must source at least the specified current to switch HIGH-to-LOW. 10. “Don’t care” indicates any valid logic level. 11 the V associated with the input side. DDI DD 12. Reflects current per supply, V © 2009 Fairchild Semiconductor Corporation FXL3SD206 • Rev. 1.0.0 (Continued) Condition =V or GND I DD_CON =0 to 3.6V O ...

Page 9

... Output Fall Time B and C Port fall I Dynamic Output Current High OHD I Dynamic Output Current Low OLD Notes: 13. See Figure 9. 14. See Figure 10. © 2009 Fairchild Semiconductor Corporation FXL3SD206 • Rev. 1.0.0 =10pF). T =-40°C to 85°C. I =2. Typ. Max. Typ. ...

Page 10

... Skew is the variation of propagation delay between output signals and applies only to output signals on the same port and switching with the same polarity (LOW to HIGH or HIGH to LOW). See Figure 12. Skew is guaranteed, but not tested. © 2009 Fairchild Semiconductor Corporation FXL3SD206 • Rev. 1.0.0 =-40°C to 85° ...

Page 11

... A Symbol Input Capacitance C IN Control Pins (OE, VDD_SEL, CH_SEL) Dn_A, CMD_A,CLK_A Input/Output C I/O Capacitance Dn_BC, CMD_B, CMD_C, CLK_BC C Power Dissipation Capacitance PD © 2009 Fairchild Semiconductor Corporation FXL3SD206 • Rev. 1.0.0 V =2.8V to 3.6V V =2.3V to 2.7V V DD_n DD_n Min. 100 100 100 100 80 80 Parameter V V CH_SEL=V ...

Page 12

... Figure 6. Waveform for Inverting and Non-Inverting Functions Notes: 17. Input 2.0ns, 10 18. Input 2.5ns, 10 © 2009 Fairchild Semiconductor Corporation FXL3SD206 • Rev. 1.0 TEST DUT SIGNAL C1 Figure 5. AC Test Circuit Input Signal Data Pulses 0V V CCI ...

Page 13

... Figure 8. 3-State Output High Enable Time for Low Voltage Logic Notes: 21. Input 2.0ns, 10 22. Input 2.5ns, 10 Symbol © 2009 Fairchild Semiconductor Corporation FXL3SD206 • Rev. 1.0 PZL DATA V Y OUT = 3.0V to 3.6V only PZH DATA V x OUT = 3.0V to 3.6V only ...

Page 14

... V I OHD Figure 9. Active Output Rise Time and Dynamic Output Current High V I OHD Figure 10. OUTPUT OUTPUT © 2009 Fairchild Semiconductor Corporation FXL3SD206 • Rev. 1.0.0 t rise 80 OUT 20 CCO V OL Time Δ V ≈ + × OUT = + ( ) ( Δ ...

Page 15

... Package specifications do not expand the terms of Fairchild’s worldwide terms and conditions, specifically the warranty therein, which covers Fairchild products. Always visit Fairchild Semiconductor’s online packaging area for the most recent package drawings: http://www.fairchildsemi.com/packaging/. © 2009 Fairchild Semiconductor Corporation FXL3SD206 • Rev. 1.0 2.50 3.40 ...

Page 16

... Fairchild Semiconductor Corporation FXL3SD206 • Rev. 1.0.0 16 www.fairchildsemi.com ...