nsbmc290 National Semiconductor Corporation, nsbmc290 Datasheet

nsbmc290

Related parts for nsbmc290

nsbmc290 Summary of contents

Page 1

... C 1995 National Semiconductor Corporation TL V 11803 to the The function of NSBMC290 is to interface the page mode access protocol of dynamic RAMs with the more general burst mode access protocol supported by the Am29000 lo- cal channel The device manages a double banked arrang- ment of dynamic RAMs such that when burst accesses are ...

Page 2

... Connection Diagrams PQFP Order Number NSBMC290VF NS Package Number VF132A PGA Bottom View Order Number NSBMC290UP See NS Package Number UP124A 11803 – 11803 – 9 ...

Page 3

Pin Descriptions PGA Pin QFP Pin Signal A10 ...

Page 4

... NSBMC290 to accept a data request OPT0 – 2 Data Options (Input Active Low) These inputs specify the data transfer size and operating mode The NSBMC290 responds only to cycles in which the values are asserted The use of these signals is compatible with the specifications for In-Circuit Emulators PDA ...

Page 5

... Pin Descriptions (Continued) MEMORY INTERFACE The NSBMC290 is designed to drive a memory array orga- nized as 2 banks each of 32 bits The address and control signals for the memory array are output through high current Pin A(A B)0 – 10 Multiplexed Addresses (Output High Current) These two buses transfer the multiplexed row and column ...

Page 6

... RSTOUT from one chip connecting to RESET of the next chip When a NSBMC290 has been configured it deasserts the RSTOUT signal allowing the next NSBMC290 in the chain to then be configured All NSBMC290 devices must be configured be- fore memory accesses are attempted ...

Page 7

... The transfer of Instructions and Data from the memory sub- system to the Local Channel occurs through buffers con- trolled by the NSBMC290 Of the six signals provided for this purpose four operate in multiple modes the remaining two (DBLeA DBLeB) have fixed interpretation These two ...

Page 8

... DRAM SIZE This two bit field bit 7 and bit 6 configures the NSBMC290 for the correct memory address size and hence total mem- ory block size Note that the memory in both banks of the ...

Page 9

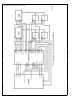

... For mixed instruction and data designs all local channel signals must be connected Tables V and VI detail the con- trol signal sets required for the NSBMC290 to control the corresponding address spaces It is recommended that all control signals be connected and that instruction and data ...

Page 10

Typical Application (Continued) 10 ...

Page 11

... SIMPLE ACCESS SEQUENCE The NSBMC290 can return data to the processor in only 4 clocks or 5 clocks for a simple access depending on the mode chosen (Configuration Bit 17) If multiple access DBTX DBTXa DBTXb DBCE DBCEa DBCEb IBTX IBTXa IBTXb ...

Page 12

... Figure 5 This access se- quence will continue until either canceled or suspended by the Am29000 or normal burst termination occurs The NSBMC290 will preempt the burst sequence only in the case that a refresh cycle has been requested and has been outstanding for a time in excess of 80% of the refresh peri- ...

Page 13

Absolute Maximum Ratings If Military Aerospace specified devices are required please contact the National Semiconductor Sales Office Distributors for availability and specifications Supply Voltage ( Input Voltage ( Input Current ...

Page 14

Timing Parameters DBTX DBTXa DBTXb DBCE DBCEa DBCEb IBTX IBTXa IBTXb FIGURE 5 Simple Access Timing 11803 – 10 ...

Page 15

AC Timing Parameters (Unless otherwise stated V Symbol Description 1 t BlNV Setup BSU 2 t BINV Hold Request Sync Setup Time RQSU 4 t Request Sync Hold Time RQH 5 t Synchronous Input Setup SU 5A ...

Page 16

AC Timing Parameters (Continued TXa IBTXa DBTXa CEa IBCEa DBCE TXb Note Buffer control signal timing is illustrated using the mode dependent signal naming convention (See page shown the switching behavior is typical of ...

Page 17

... Release Notes for NSBMC290 Revision ‘‘A’’ A NOTE ON THE OPERATION OF THE Am29000 characteristic of the Am29000 (Rev D) that it can de- assert the IBREQ signal independently of the current state of IRDY and IBACK The V29BMC (Rev A) accommo- dates this behavior in all cases with one exception ...

Page 18

Ordering Code Information National Semiconductor Mode Burst Mode Controller Processor e 290 AMD 29000 Family NS BMC 290 Frequency 16 MHz 20 MHz 25 MHz 33 MHz Packaging 124-Lead PPGA 132-Lead PQFP ...

Page 19

... Physical Dimensions inches (millimeters) Pin Grid Array (PGA) Order Number NSBMC290UP NS Package Number UP124A 19 ...

Page 20

... National does not assume any responsibility for use of any circuitry described no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications Plastic Quad Flatpak (PQFP) Order Number NSBMC290VF NS Package Number VF132A 2 A critical component is any component of a life ...