am79c972b Advanced Micro Devices, am79c972b Datasheet

am79c972b

Available stocks

Related parts for am79c972b

am79c972b Summary of contents

Page 1

Am79C972 PCnet™-FAST+ Enhanced 10/100 Mbps PCI Ethernet Controller with OnNow Support DISTINCTIVE CHARACTERISTICS n Integrated Fast Ethernet controller for the Peripheral Component Interconnect (PCI) bus — 32-bit glueless PCI host interface — Supports PCI clock frequency from ...

Page 2

Supports megabyte (Mbyte) optional Boot PROM or Flash for diskless node application n Look-Ahead Packet Processing (LAPP) data handling technique reduces system overhead by allowing protocol analysis to begin before the end of a receive frame ...

Page 3

™ ™ ...

Page 4

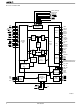

BLOCK DIAGRAM CLK RST AD[31:0] C/BE[3:0] PAR FRAME TRDY IRDY STOP IDSEL DEVSEL PCI Bus REQ Interface GNT Unit PERR SERR INTA Buffer Management Unit TCK JTAG TMS Port TDI Control TDO 4 EBUA_EBA[7:0] EBDA[15:8] EBD[7:0] EROMCS AS_EBOE EBWE EBCLK ...

Page 5

TABLE OF CONTENTS AM79C972 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ...

Page 6

USER ACCESSIBLE REGISTERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ...

Page 7

RELATED AMD PRODUCTS Part No. Description Am79C90 CMOS Local Area Network Controller for Ethernet (C-LANCE) Am7996 IEEE 802.3/Ethernet/Cheapernet Tap Transceiver Am79C98 Twisted Pair Ethernet Transceiver (TPEX) Am79C100 Twisted Pair Ethernet Transceiver Plus (TPEX+) Am79865 100 Mbps Physical Data Transmitter (PDT) ...

Page 8

... AD15 31 VSS 32 AD14 33 AD13 34 VSSB 35 AD12 36 AD11 37 VDD_PCI 38 AD10 39 AD9 40 Pin 1 is marked for orientation. 8 PCnet“-FAST+ Am79C972BKC Am79C972 Am79C972 EEDO/LED3/SRD/MIIRXFRTGD 120 PHY_RST 119 118 MDIO VSSB 117 116 MDC 115 RXD3 RXD2 114 113 VDDB 112 RXD1 111 RXD0/RXFRTGD ...

Page 9

... AD14 36 AD13 37 VSSB 38 AD12 39 AD11 40 VDD_PCI 41 AD10 42 AD9 Pin 1 is marked for orientation. PCnet“-FAST+ Am79C972 Am79C972BVC Am79C972 132 NC 131 NC EEDO/LED3/SRD/MIIRXFRTGD 130 129 PHY_RST 128 MDIO 127 VSSB MDC 126 125 RXD3 124 RXD2 VDDB 123 122 RXD1 ...

Page 10

PIN DESIGNATIONS (PQR160) Listed By Pin Number Pin Pin Pin Pin No. Name No. Name 1 IDSEL 41 AD8 2 AD23 42 C/BE0 3 VSSB 43 VSSB 4 AD22 44 AD7 5 VDD_PCI 45 VDD_PCI 6 AD21 46 AD6 7 ...

Page 11

PIN DESIGNATIONS (PQL176) Listed By Pin Number Pin Pin Pin Pin No. Name No. Name IDSEL 47 AD8 4 AD23 48 C/BE0 5 VSSB 49 VSSB 6 AD22 50 AD7 7 ...

Page 12

PIN DESIGNATIONS (PQR160, PQL176) Listed By Group Pin Name Pin Function PCI Bus Interface AD[31:0] Address/Data Bus C/BE[3:0] Bus Command/Byte Enable CLK Bus Clock DEVSEL Device Select FRAME Cycle Frame GNT Bus Grant IDSEL Initialization Device Select INTA Interrupt IRDY ...

Page 13

PIN DESIGNATIONS Listed By Group Pin Name Pin Function Media Independent Interface (MII) COL Collision CRS Carrier Sense MDC Management Data Clock MDIO Management Data I/O RX_CLK Receive Clock RXD[3:0] Receive Data RX_DV Receive Data Valid RX_ER Receive Error TX_CLK ...

Page 14

Listed By Driver Type The following table describes the various types of out- put drivers used in the Am79C972 controller. All I I values shown in the table apply to 3.3 V signaling. OH Name Type LED LED OMII1 Totem ...

Page 15

... K = Plastic Quad Flat Pack (PQR160 Thin Quad Flat Pack (PQL176) SPEED OPTION Not applicable DEVICE NUMBER/DESCRIPTION Am79C972B PCnet-FAST+ Enhanced 10/100 Mbps PCI Ether- net Controller with OnNow Support Valid Combinations Valid Combinations list configurations planned to be supported in volume for this device. Consult the local ...

Page 16

PIN DESCRIPTIONS PCI Interface AD[31:0] Address and Data Address and data are multiplexed on the same bus in- terface pins. During the first clock of a transaction, AD[31:0] contain a physical address (32 bits). During the subsequent clocks, AD[31:0] contain ...

Page 17

INTA Interrupt Request An attention signal which indicates that one or more of the following status flags is set: EXDINT, IDON, MERR, MISS, MFCO, MPINT, RCVCCO, RINT, SINT, TINT, TXSTRT, UINT, MCCINT, MPDTINT, MAPINT, MRE- INT, and STINT. Each status ...

Page 18

REQ Bus Request The Am79C972 controller asserts REQ pin as a signal that it wishes to become a bus master. REQ is driven high when the Am79C972 controller does not request the bus. In Power Management mode, the REQ pin ...

Page 19

HIGH, the output is a totem pole driver. Note: The LED1 pin is multiplexed with the EESK and SFBD pins. The LED1 pin is also used during EEPROM Auto- Detection to determine whether or not ...

Page 20

TBC_EN Time Base Clock Enable TBC_EN is an input that controls the selection of the source of ...

Page 21

D flip-flop. During subsequent cycles of a boot device access, address bits [7:0] are present on these pins. All EBUA_EBA[7:0] outputs are forced to a constant level to conserve power while no access on the Expan- sion ...

Page 22

COL Collision COL is an input that indicates that a collision has been detected on the network medium. Note: The COL pin is multiplexed with the CLSN pin. CRS Carrier Sense CRS is an input that indicates that a non-idle ...

Page 23

General Purpose Serial Interface CLSN Collision CLSN is an input that indicates a collision has occurred on the network. Note: The CLSN pin is multiplexed with the COL pin. RXCLK Receive Clock RXCLK is an input. The rising edges of ...

Page 24

SRD Serial Receive Data SRD is the decoded NRZ data from the network when in GPSI mode. This signal can be used for external ad- dress detection. Note: When the MII port is selected, SRD will not gen- erate transitions ...

Page 25

Power Supply Pins VDDB I/O Buffer Power (7 Pins) There are seven power supply pins that are used by the input/output buffer drivers. All VDDB pins must be con- nected to a +3.3 V supply. VDD_PCI PCI I/O Buffer Power ...

Page 26

BASIC FUNCTIONS System Bus Interface The Am79C972 controller is designed to operate as a bus master during normal operations. Some slave I/O accesses to the Am79C972 controller are required in nor mal operations as well. Initialization of the Am79C972 controller ...

Page 27

DETAILED FUNCTIONS Slave Bus Interface Unit The slave bus interface unit (BIU) controls all accesses to the PCI configuration space, the Control and Status Registers (CSR), the Bus Configuration Registers (BCR), the Address PROM (APROM) locations, and the Expansion ROM. ...

Page 28

CLK FRAME AD ADDR 1010 C/BE BE PAR PAR IRDY TRDY DEVSEL STOP IDSEL DEVSEL is sampled Figure 1. Slave Configuration Read The Am79C972 controller will not assert DEVSEL if it detects an address match, but ...

Page 29

CLK FRAME ADDR AD C/BE 0010 PAR PAR IRDY TRDY DEVSEL STOP Figure 3. Slave Read Using I/O Command CLK FRAME AD ADDR 0111 C/BE PAR PAR IRDY TRDY DEVSEL STOP Figure ...

Page 30

Expansion ROM Transfers The host must initialize the Expansion ROM Base Ad- dress register at offset 30H in the PCI configuration space with a valid address before enabling the access to the device. The Am79C972 controller will not react to ...

Page 31

During the boot procedure, the system will try to find an Expansion ROM. A PCI system assumes that an Ex- pansion ROM is present when it reads the ROM signa- ture 55H (byte 0) and AAH (byte 1). Slave Cycle ...

Page 32

If the host is not yet ready when the Am79C972 control- ler asserts TRDY, the device will wait for the host to as- sert IRDY. When the host asserts IRDY and FRAME is still asserted, the Am79C972 controller will finish ...

Page 33

CLK 1 FRAME AD C/BE PAR PERR IRDY TRDY DEVSEL Figure 10. Slave Cycle Data Parity Error Response Master Bus Interface Unit The master Bus Interface Unit (BIU) controls the acqui- sition of the PCI bus and all accesses to ...

Page 34

Figure 11 shows the Am79C972 controller bus acquisi- tion. REQ is asserted and the arbiter returns GNT while an othe tran sfer dat Am79C972 controller ...

Page 35

CLK FRAME ADDR DATA AD 0000 C/BE 0110 PAR PAR IRDY TRDY DEVSEL REQ GNT DEVSEL is sampled Figure 12. Non-Burst Read Transfer CLK FRAME AD ADDR 1110 C/BE PAR PAR IRDY ...

Page 36

Basic Non-Burst Write Transfer By default, the Am79C972 controller uses non-burst cy cles bus ma ster wr ite operations. All Am79C972 controller non-burst write accesses are of the PCI command type Memory Write (type 7). The ...

Page 37

Figure 15 shows a typical burst write access. The Am79C972 controller arbitrates for the bus, is granted access, and writes four 32-bit words (DWords) to the system memory and then releases the bus. In this ex- ample, the memory system ...

Page 38

CLK 1 2 FRAME AD ADDR i C/BE PAR IRDY TRDY DEVSEL STOP REQ GNT DEVSEL is sampled Figure 16. Disconnect With Data Transfer Disconnect Without Data Transfer Figure 17 shows a target disconnect sequence during which no data is ...

Page 39

CLK 1 2 FRAME AD C/BE PAR IRDY TRDY DEVSEL STOP REQ GNT DEVSEL is sampled Figure 17. Disconnect Without Data Transfer RTABORT (PCI Status register, bit 12) will be set to indicate that the Am79C972 controller has received a ...

Page 40

CLK FRAME AD ADDR DATA 0000 0111 C/BE PAR PAR IRDY TRDY DEVSEL STOP REQ GNT DEVSEL is sampled Figure 18. Target Abort When the preemption occurs after the counter has counted down to 0, the ...

Page 41

CLK FRAME ADDR AD C/BE 0111 PAR PAR IRDY TRDY DEVSEL REQ GNT DEVSEL is sampled Figure 19. Preemption During Non-Burst Transaction CLK FRAME AD ADDR DATA DATA C/BE 0111 PAR PAR ...

Page 42

CLK FRAME AD C/BE PAR IRDY TRDY DEVSEL REQ GNT CLK FRAME AD C/BE PAR PERR IRDY TRDY DEVSEL Figure 22. Master Cycle Data Parity Error Response ADDR DATA 0111 0000 PAR DEVSEL ...

Page 43

Whenever the Am79C972 controller is the current bus master and a data parity error occurs, SINT (CSR5, bit 11) will be set to 1. When SINT is set, INTA is asserted if the enable bit SINTE (CSR5, bit 10) is ...

Page 44

CLK 1 FRAME AD C/BE PAR IRDY TRDY DEVSEL REQ GNT DEVSEL is sampled Figure 23. Initialization Block Read In Non-Burst Mode FRAME C/BE IRDY TRDY DEVSEL REQ GNT Figure 24. Initialization Block Read In Burst Mode ...

Page 45

Descriptor DMA Transfers Am79C972 microcode will determine when a descrip- tor access is required. A descriptor DMA read will con- sist of two data transfers. A descriptor DMA write will consist of one or two data transfers. The descriptor DMA ...

Page 46

CLK 1 FRAME AD C/BE PAR IRDY TRDY DEVSEL REQ GNT DEVSEL is sampled Figure 25. Descriptor Ring Read In Non-Burst Mode CLK FRAME AD C/BE PAR IRDY TRDY DEVSEL REQ GNT Figure 26. Descriptor Ring Read In Burst Mode ...

Page 47

Table 5. Descriptor Write Sequence SWSTYLE BWRITE BCR20[7:0] BCR18[5] AD Bus Sequence Address = XXXX XX04h Data = MD2[15:0], MD1[15: Idle Address = XXXX XX00h Data = MD1[31:24] Address = XXXX XX08h Data = MD2[31: Idle ...

Page 48

CLK 1 FRAME AD C/BE PAR IRDY TRDY DEVSEL REQ GNT DEVSEL is sampled Figure 27. Descriptor Ring Write In Non-Burst Mode CLK FRAME AD C/BE PAR IRDY TRDY DEVSEL REQ GNT Figure 28. Descriptor Ring Write In Burst Mode ...

Page 49

Burst FIFO DMA Transfers Bursting is only performed by the Am79C972 controller if the BREADE and/or BWRITE bits of BCR18 are set. These bits individually enable/disable the ability of the Am79C972 controller to perform burst accesses during master read operations ...

Page 50

CLK FRAME ADD AD DATA DATA 0111 0000 C/BE PAR PAR PAR IRDY TRDY DEVSEL REQ GNT DEVSEL is sampled Figure 30. FIFO Burst Write At End Of Unaligned Buffer The exact number of total transfer ...

Page 51

CSR15, and then setting the START bit in CSR0. Note that this form of restart will not perform the same in the Am79C972 controller as in the C-LANCE device. In particular, upon restart, the Am79C972 controller re- loads the ...

Page 52

Note that even though the Am79C972 controller treats the descriptor entries as 16-bit structures, it will always perform 32-bit bus transfers to access the descriptor entries. The value of CSR2, bits 15-8, ...

Page 53

CSR2 CSR1 IADR[31:16] IADR[15:0] Initialization Block MOD PADR[15:0] PADR[31:16] PADR[47:32] LADRF[15:0 LADRF[31:16] LADRF[47:32] LADRF[63:48] RDRA[15:0] RLE RES RDRA[23:16] TDRA[15:0] TDRA[23:16] TLE RES Note that the value of CSR2, bits 15-8, is used as the upper 8-bits for all memory addresses ...

Page 54

CSR2 CSR1 IADR[31:16] IADR[15:0] Initialization Block TLE RES RLE RES MODE PADR[31:0] RES PADR[47:32] LADRF[31:0 LADRF[63:32] RDRA[31:0] TDRA[31:0] If RXON is cleared to 0, the Am79C972 controller will never poll RDTE locations. In order to avoid missing frames, the ...

Page 55

TDTE location in the ring. If the OWN bit is set and the buffer length is 0, the OWN bit will be cleared. In the C-LANCE device, the buffer length ...

Page 56

It then decides whether to ac- cept or reject the frame based on all active addressing schemes. If the frame is accepted, the Am79C972 con- troller checks the current receive buffer status register CRST (CSR41) to ...

Page 57

Media Access Control The Media Access Control (MAC) engine incorporates the essential protocol requirements for operation of an Ethernet/IEEE 802.3-compliant node and provides the interface between the FIFO subsystem and the MII. This section describes operation of the MAC engine ...

Page 58

Error Detection The MAC engine provides several facilities which re- port and recover from errors on the medium. In addi- tion, it protects the network from gross errors ...

Page 59

To enhance system robustness, the following optional measures, as specified in 4.2.8, are recommended when Inter- Frame-SpacingPart1 is other than 0: 1. Upon completing a transmission, start timing the in- terrupted gap, as soon ...

Page 60

Collision Handling Collision detection is performed and reported to the MAC engine via the COL/CLSN input pin collision is detected before the complete preamble/ SFD sequence has been transmitted, the MAC engine will complete the preamble/SFD before appending ...

Page 61

The pad is placed between the LLC data field and FCS field in the IEEE 802.3 frame. FCS is always added if the frame is padded, regardless of the state of DXMTFCS (CSR15, bit 3) or ADD_FCS (TMD1, ...

Page 62

FIFO can be overwritten as soon transmitted total attempts (initial attempt plus 15 retries) fail, the Am79C972 controller sets the RTRY bit in the cur- rent transmit TDTE in host memory ...

Page 63

SFD) must match the least signif- icant byte of CSR12 (PADR[7:0]), and the sixth byte re- ceived must match the most significant byte of CSR14 (PADR[47:40]). ...

Page 64

Bits Bits Preamble SFD Destination 1010....1010 10101011 Start of Frame at Time = 0 Increasing Time Figure 34. IEEE 802.3 ...

Page 65

The controller pro- vides two basic types of loopback. In internal loopback mode, the transmitted data is looped back to the re- ceiver inside ...

Page 66

TXDAT and RXDAT pins of the GPSI port, and the TXD[3:0] and RXD[3:0] pins of the MII port. Full-duplex operation is enabled by the FDEN bit located in BCR9 for all ports. ...

Page 67

Media Independent Interface The Am79C972 controller fully supports the MII ac- cording to the IEEE 802.3 standard. This Reconcilia- tion Sublayer interface allows a variety of PHYs ( ...

Page 68

NULL events. Cer- tain in band non-IEEE 802.3u-compliant flow control sequences may cause erratic behavior for the Am79C972 controller. Consult the switch/bridge/router/ hub manual to disable the in-band flow control se- quences if they are ...

Page 69

Am79C972 controller had an MII management frame read error and that the data in BCR34 is not valid. The data field to/from the external PHY is read or written into the BCR34 register. The last ...

Page 70

Automatic Network Selection: Exceptions If ASEL (BCR2, bit 0) is set DANAS (BCR 32, bit 7) is set to 1, then the Network Port Manager will dis- continue actively trying to establish the connections assumed ...

Page 71

After the RESET bit is cleared, then the normal flow continues. External Address Detection Interface The EADI is provided to allow external address filtering and to provide a Receive Frame Tag word for propri- etary routing information. ...

Page 72

Table 8. EADI Operations Required PROM EAR Timing No timing 1 X requirements No timing 0 1 requirements Low for two bit 0 0 times plus 10 ns External Address Detection Interface: External PHY When using the MII, the EADI ...

Page 73

RX_CLK RX_DV SF/BD MIIRXFRTGE MIIRXFRTGD SRDCLK SRD SFBD MIIRXFRTGE MIIRXFRTGD Note: Bitz is last data bit. Expansion Bus Interface The Am79C972 controller contains an Expansion Bus Interface that supports Flash and EPROM devices as boot devices, as well as provides ...

Page 74

AS_EBOE is driven high for EBUA_EBA[7:0] are driven with the upper 8 bits of the Expansion ROM address for one more clock cycle after AS_EBOE goes low. Next, the Am79C972 controller starts driving the lower 8 bits of the Expansion ...

Page 75

Flash/EPRO in- puts (t ) from the time defined by ROMTMG: s_D t = ROMTMG * CLK period * CLK_FAC - (t ACC (t ) s_D The timing diagram in Figure 42 ...

Page 76

Am79C972 EBUA_EBA[7:0] EROMCS EBDA[15:8] AS_EBOE Figure 41. EPROM Only Configuration for the Expansion Bus (>64K EPROM) Since setting MEMEN also enables memory mapped access to the I/O resources, attention must be given to the PCI Memory Mapped I/O Base Address ...

Page 77

CLK EBUA_EBA [7:0] Latched Address EBDA [15:8] EBD AS_EBO EROMCS FRAME IRDY TRDY DEVSEL Figure 42. Expansion ROM Bus Read Sequence CLK EBUA_EBA[7:0] EBDA[15:8] EBD[7:0] EROMCS AS_EBOE Figure 43. Flash Read from Expansion Bus Data Port The EROMCS ...

Page 78

CLK EBUA_EBA[7:0] EBDA[15:8] EBD[7:0] EROMCS AS_EBOE EBWE Figure 44. Flash Write from Expansion Bus Data Port AMD Flash Programming AMD’s Flash products are programmed on a byte-by- byte basis. Programming is a four bus cycle operation. There are two “unlock” ...

Page 79

SRAM Configuration The Am79C972 controller supports SRAM as a FIFO extension as well as providing a read/write data path to the SRAM. The Am79C972 controller contains 12 Kbytes of SRAM. Internal SRAM Configuration The SRAM_SIZE (BCR25, bits 7-0) programs the ...

Page 80

PCI Bus Interface Unit Buffer Management Unit Figure 45. Block Diagram No SRAM Configuration PCI Bus Interface Unit Buffer Management Unit Figure 46. Block Diagram Low Latency Receive Configuration 80 Bus MAC Rcv Rcv FIFO FIFO MAC Bus Xmt ...

Page 81

EEPROM Interface The Am79C972 controller contains a built-in capability for reading and writing to an external serial 93C46 EEPROM. This built-in capability consists of an inter- face for direct connection to a 93C46 compatible EEPROM, an automatic EEPROM read feature, ...

Page 82

BCR37 PCI DATA Register Zero (DATA0) Alias Register n BCR38 PCI DATA Register One (DATA1) Alias Register n BCR39 PCI DATA Register Two (DATA2) Alias Register n BCR40 PCI DATA (DATA3) Alias Register n BCR41 PCI DATA Register Four ...

Page 83

Word Byte Address Address Most Significant Byte 2nd byte of the ISO 8802-3 (IEEE/ANSI 802.3) 00h* 01h station physical address for this node. 01h 03h 4th byte of the node address 02h 05h 6th byte of the node address 03h ...

Page 84

Table 11. LED Default Configuration LED Output Indication Driver Mode Open Drain - LED0 Link Status Active Low Receive Open Drain - LED1 Status Active Low Open Drain - LED2 -- Active Low Transmit Open Drain - LED3 Status Active ...

Page 85

Magic Packet MPPEN PG MPMODE MPEN Link Change LCMODE Link Change H_RESET Pattern Match BCR47 BCR46 Input Pattern Pattern Match RAM (PMR) When the software determines that the signal came from the PCnet-FAST+ device, it writes to the device’s PMCSR ...

Page 86

PME_STATUS bit (PMCSR, bit 15 set, which in tur n will asser t the PME pin if the PME_EN bit (PMCSR, bit 8) is set. Pattern Match RAM (PMR) PMR is organized as an array of 64 words ...

Page 87

BCR 47 BCR Bit Number PMR_B4 Pattern Match RAM Address pointer 1 P7 pointer 2 Data Byte 3 2+n Data Byte 4n+3 Date Byte 4n+2 J Data Byte 3 J+m Data Byte ...

Page 88

MPSE (BCR4-7, bit 9) must be set enable that function. Note: The polarity of the LED pin can be programmed to be active HIGH by setting LEDPOL (BCR4-7, bit 14 Once a Magic Packet frame ...

Page 89

Other Data Registers Other data registers are the following: 1. Bypass Register (1 bit) 2. Device ID register (32 bits) (Table 14). Table 14. Device ID Register Bits 31-28 Version Bits 27-12 Part Number (0010 0110 0010 0100) Manufacturer ID. ...

Page 90

NAND Tree Input No. Pin No. Name 1 143 RST 2 144 CLK 3 145 GNT 4 146 REQ 5 148 AD31 6 151 AD30 7 152 AD29 8 153 AD28 9 154 AD27 10 156 AD26 11 158 AD25 ...

Page 91

Reset There are four different types of RESET operations that may C972 devi c e, H_RESET, S_RESET, STOP, and POR. The following is a description of each ...

Page 92

Table 16 Device ID Status Base-Class Sub-Class Reserved Header Type Memory Mapped I/O Base Address Subsystem ID Expansion ROM Base Address Reserved MAX_LAT MIN_GNT PMC DATA_REG PMCSR_BSE The Am79C972 controller supports mapping the ad- dress space to ...

Page 93

The six bytes of the IEEE station address occupy the first six locations of the Address PROM space. The next six bytes are reserved. Bytes 12 and 13 ...

Page 94

Table 18. Legal I/O Accesses in Word I/O Mode (DWIO = 0) AD[4:0] BE[3:0] Type 0XX00 1110 RD 0XX01 1101 RD 0XX10 1011 RD 0XX11 0111 RD 0XX00 1100 RD 0XX10 0011 RD 10000 1100 RD 10010 0011 RD 10100 ...

Page 95

USER ACCESSIBLE REGISTERS The Am79C972 controller has three types of user reg- isters: the PCI configuration registers, the Control and Status registers (CSR), and the Bus Control registers (BCR). The Am79C972 controller implements all PCnet-ISA (Am79C960) registers, all C-LANCE (Am79C90) ...

Page 96

CSR125^ MAC Enhanced Configuration Control BCR2^ Miscellaneous Configuration BCR4^ LED0 Status BCR5^ LED1 Status BCR6^ LED2 Status BCR7^ LED3 Status BCR9^ Full-Duplex Control BCR18^ Bus and Burst Control BCR19 EEPROM Control and Status BCR20 Software Style BCR22^ PCI Latency BCR23^ ...

Page 97

PC net 79C9 70A ) Cnet - FAS T (Am79C971) devices. The PCI Device ID register is located at offset 02h in the PCI Configuration Space read only. PCI Command ...

Page 98

MEMEN. The Am79C972 controller will only respond to ac- cesses to the Expansion ROM when both ROMEN (PCI Expan- sion ROM Base Address register, bit 0) and MEMEN are set to 1. Since MEMEN ...

Page 99

RTABORT Am79C972 cleared by writing a 1. Writing a 0 has no effect. RTABORT is cleared by H_RESET and is not affected by S_RESET or by set- ting the STOP bit. 11 STABORT Send Target Abort. Read as ze- ro; ...

Page 100

PCI Base-Class Register Offset 0Bh The PCI Base-Class register is an 8-bit register that broadly classifies the function of the Am79C972 con- troller. The value of this register is 02h which classifies the Am79C972 device as a network controller. The ...

Page 101

RES Reserved location. Read as zero; write operations have no effect. 0 IOSPACE I/O space indicator. Read as one; write operations have no effect. Indicating that this base address register describes an I/O base address. PCI Memory Mapped I/O ...

Page 102

PCI Expansion ROM Base Address Register Offset 30h The PCI Expansion ROM Base Address register is a 32-bit register that defines the base address, size and address alignment of an Expansion ROM located at offset 30h in the ...

Page 103

It is cleared by H_RESET and is not affected by S_RESET or by setting the STOP bit. PCI Interrupt Pin Register Offset 3Dh This PCI Interrupt Pin register is an 8-bit register that indicates the interrupt pin that ...

Page 104

D2_SPT D2 Support. If this bit this function supports the D2 Power Management State. Read only. 9 D1_SPT D1 Support. If this bit this function supports the D1 Power Management State. Read only. ...

Page 105

PME_EN PME Enable. PME_EN enables the function to assert PME. When a 0, PME as- sertion is disabled. This bit defaults to “0” if the func- tion does not support PME gener- ation from D3cold. If the function supports ...

Page 106

Am79C972 control registers. A read access will yield undefined values. Read/Write accessible always. RAP is cleared by H_RESET or S_RESET and is unaffected by setting the STOP bit. Control and Status Registers The CSR space is accessible by performing accesses ...

Page 107

When MERR is set, INTA is as- serted if IENA is 1 and the mask bit MERRM (CSR3, bit 11 MERR assertion will set the ERR bit, regardless of the settings of IENA and MERRM. Read/Write accessible always. ...

Page 108

RXON will not be set until after the initialization block has been read in. Read accessible always. RXON is read only. RXON is cleared by H_RESET or S_RESET and set- ting the STOP bit. 4 TXON Transmit On indicates that ...

Page 109

Read/Write accessible only when either the STOP or the SPND bit is set. Unaffected by H_RESET or S_RESET setting the STOP bit. CSR2: Initialization Block Address 1 Bit Name Description 31-16 RES Reserved locations. Written as zeros and ...

Page 110

S_RESET and is not affected by STOP. 9 TINTM Transmit Interrupt TINTM is set, the TINT bit will be masked and unable to set the INTR bit. Read/Write accessible always. TINTM is cleared by H_RESET or S_RESET and is ...

Page 111

When the STP bit is found to be true, and the descrip- tor that contains this setting is owned by the Am79C972 control- ler, then the Am79C972 control- ler will stop advancing ...

Page 112

CSR4: Test and Features Control Certain bits in CSR4 indicate the cause of an interrupt. The register is designed so that these indicator bits ...

Page 113

Writing UNIT will clear UNITCMD and stop interrupts. Read/Write accessible always. UINTCMD H_RESET or S_RESET or by setting the STOP bit. 6 UINT User Interrupt. UINT is set by the Am79C972 controller after the host has issued ...

Page 114

Read/Write accessible always. LTINTEN is H_RESET or S_RESET and is unaffected by STOP. 13-12 RES Reserved locations. Written as zeros and read as undefined. 11 SINT System Interrupt is set by the Am79C972 controller when it de- tects a system ...

Page 115

Am79C972 con- troller receives a Magic Packet frame. When MPINT is set to 1, INTA is asserted if IENA (CSR0, bit 6) and the enable bit MPINTE are set to 1. Read/Write accessible always. MPINT is cleared ...

Page 116

H_RESET, S_RESET, or STOP. 11-8 RLEN Contains a copy of the receive encoded ring length (RLEN) read from the initialization block during Am79C972 controller initializa- tion. This field is written during the Am79C972 controller initial- ization routine. Read accessible ...

Page 117

S_RESET or by setting the STOP bit. 13 RDMD Receive Demand, when set, causes the Buffer Management Unit to access the Receive De- scriptor Ring without waiting for the receive poll-time counter to elapse. If RXON is not ...

Page 118

H_RESET and is not affected by S_RESET or setting the STOP bit 7 MAPINT MII Management Auto-Poll Inter- rupt. The MII Auto-Poll interrupt is set by the Am79C972 controller to indicate that the currently read status does not match the ...

Page 119

For in- stance, when MCCIINTE is set to 1 and the Auto-Poll state ma- chine generates a MII manage- ment frame, the MCCIINT will set the INTR bit upon completion of the MII management frame re- gardless of ...

Page 120

Read/Write accessible only when either the STOP or the SPND bit is set. These bits are unaffected by H_RESET, S_RESET, or STOP. CSR12: Physical Address Register 0 Note: Bits 15-0 in this register ...

Page 121

Read/Write accessible only when either the STOP or the SPND bit is set. 14 DRCVBC Disable Receive When set, Am79C972 controller from re- ceiving broadcast Used for protocols that do not support broadcast addressing, except as a function of multicast. ...

Page 122

This bit was called DTCR in the LANCE (Am7990) device. Read/Write accessible only when either the STOP or the SPND bit is set. 2 LOOP Loopback Enable allows the Am79C972 controller to operate in full-duplex mode for test pur- poses. ...

Page 123

Read/Write accessible only when either the STOP or the SPND bit is set. These bits are unaffected by H_RESET, S_RESET, or STOP. CSR20: Current Transmit Buffer Address Lower Bit Name Description 31-16 RES Reserved locations. Written as zeros and read ...

Page 124

Read/Write accessible only when either the STOP or the SPND bit is set. These bits are unaffected by H_RESET, S_RESET, or STOP. CSR27: Next Receive Descriptor Address Upper Bit Name Description 31-16 RES Reserved locations. Written as zeros and read ...

Page 125

Read/Write accessible only when either the STOP or the SPND bit is set. These bits are unaffected by H_RESET, S_RESET, or STOP. CSR34: Current Transmit Descriptor Address Lower Bit Name Description 31-16 RES Reserved locations. Written as zeros and read ...

Page 126

CSR40: Current Receive Byte Count Bit Name Description 31-16 RES Reserved locations. Written as zeros and read as undefined. 15-12 RES Reserved locations. Read and written as zeros. 11-0 CRBC Current Receive Byte Count. This field is a copy of ...

Page 127

CSR46: Transmit Poll Time Counter Bit Name Description 31-16 RES Reserved locations. Written as zeros and read as undefined. 15-0 TXPOLL Transmit Poll Time Counter. This counter is incremented by the Am79C972 controller microcode and is used to trigger the ...

Page 128

RXPOLLINT approximately represents one clock time LINT[3:0] are ignored. (RXPOL- LINT[16] is implied RXPOLLINT[15] and does not represent the sign of the two’s complement RXPOL- LINT ...

Page 129

Am7990 LANCE and Am79C960 PCnet-ISA controllers. The value of SSIZE32 is deter- mined by the Am79C972 control- ler according to the setting of the Software Style (SWSTYLE, bits 7-0 of this register). Read accessible always. SSIZE32 is read only; write ...

Page 130

SWSTYLE Style [7:0] Name LANCE/ 00h PCnet-ISA controller 01h RES PCnet-PCI 02h controller PCnet-PCI 03h controller All Other Reserved CSR61: Previous Transmit Descriptor Address Upper Bit Name Description 31-16 RES Reserved locations. Written as zeros and read as undefined. 15-0 ...