k4d263238a-gc50 Samsung Semiconductor, Inc., k4d263238a-gc50 Datasheet

k4d263238a-gc50

Related parts for k4d263238a-gc50

k4d263238a-gc50 Summary of contents

Page 1

... DDR SDRAM Double Data Rate Synchronous RAM with Bi-directional Data Strobe and DLL Samsung Electronics reserves the right to change products or specification without notice. * VDD / VDDQ=2. 32Bit x 4 Banks (144-Ball FBGA) Revision 2.0 January 2003 - 1 - 128M DDR SDRAM Rev. 2.0 (Jan. 2003) ...

Page 2

... Revision 1.4 (November 14, 2001) • Added K4D26323RA-GC36(VDD/VDDQ=2.8V) Revision 1.3 (October 22, 2001) • Corrected part number of K4D263238A-GC2A to K4D26323RA-GC2A • Changed tCDLR of -GC2A and GC33 from 3tCK to 2tCK and applied since Sept 15, 2001. • Defined x32 DDR for mobile PC graphics separately - K4D26323AA-GL** featured with VDDQ=1.8V,ICC6=1mA with reduced operating current ...

Page 3

... Changed tCDLR of K4D263238A-GC33 from 2tCK to 3tCK • Removed VDDQ=1.8V from the spec. • Added K4D263238A- low power part • Defined DC spec. Revision 0.1 (August 2, 2001) - • Changed tCK(max) of K4D263238A-GC45/-50/-55/-60 from 7ns to 10ns. Revision 0.0 (June, 2001) - Target Spec • Defined Target Specification * VDD / VDDQ=2.8V * ...

Page 4

... K4D26323RA-GC2A K4D26323RA-GC33 K4D26323RA-GC36 GENERAL DESCRIPTION FOR 1M x 32Bit x 4 Bank DDR SDRAM The K4D26323RA is 134,217,728 bits of hyper synchronous data rate Dynamic RAM organized as 4 x1,048,576 words by 32 bits, fabricated with SAMSUNG ’ extremely high performance up to 2.8GB/s/chip. I/O transactions are possible on both edges of the clock cycle. Range of operating frequencies, programmable burst length and programmable latencies allow the device to be useful for a variety of high performance memory system applications ...

Page 5

... DDQ V SSQ NC MCL - 5 - 128M DDR SDRAM DQ29 DQ28 VSSQ DM3 DQ30 VDDQ NC VDDQ VSSQ VSSQ VSSQ DQ26 VSSQ VSS VDD VDDQ VSS VSSQ VDDQ DQ15 Thermal VSS VSSQ ...

Page 6

... Isolated power supply and ground for the output buffers to provide improved noise immunity. Reference voltage for inputs, used for SSTL interface. This pin is recommended to be left "No connection" on the device Must connect low to CK pin. REF - 6 - 128M DDR SDRAM Function for DQS for ...

Page 7

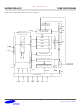

... Data Input Register Serial to parallel 64 1Mx32 1Mx32 1Mx32 1Mx32 Column Decoder Latency & Burst Length Programming Register LWE LCAS LWCBR Timing Register CS RAS CAS WE DMi - 7 - 128M DDR SDRAM LWE LDMi 64 32 x32 DQi Data Strobe (DQS0~DQS3) DLL CK,CK LDMi Rev. 2.0 (Jan. 2003) ...

Page 8

... K4D26323RA-GC FUNCTIONAL DESCRIPTION • Power-Up Sequence DDR SDRAMs must be powered up and initialized in a predefined manner to prevent undefined operations. 1. Apply power and keep CKE at low state (All other inputs may be undefined) - Apply VDD before VDDQ . - Apply VDDQ before VREF & VTT 2. Start clock and maintain stable condition for minimum 200us. ...

Page 9

... The default value of the mode register is not defined, therefore the mode register must be written after EMRS setting for proper operation. The mode register is written by asserting low on CS, RAS, CAS and WE(The DDR SDRAM should be in active mode with CKE already high prior to writing into the mode register). The state of address pins A ...

Page 10

... DLL. The extended mode register is written by assert- ing low on CS, RAS, CAS, WE and high on BA0(The DDR SDRAM should be in all bank precharge with CKE already high prior to writing into the extended mode register). The state of address pins A0 A5 A11 and BA1 in the same cycle as CS, RAS, CAS and WE going low are written in the extended mode register ...

Page 11

... DC level of the same. Peak to DDQ of the receiving device. REF < acceptable. For all other pins that are not under test 2.8V 5% DD/ DDQ 128M DDR SDRAM Value Unit -0.5 ~ 3.6 V -1.0 ~ 3.6 V -0.5 ~ 3.6 V -55 ~ +150 qC 3 ...

Page 12

... SS DD Symbol Min V V +0.4 IH REF 0 0.5*V -0.2 IX DDQ of the transmitting device and must track variations in the DC level of the same DDQ - 12 - 128M DDR SDRAM C) Version -33 -36 480 460 130 120 130 120 350 320 840 800 320 310 4 1080 1000 =2 ...

Page 13

... IN1 C IN2 C IN3 ~ OUT C IN4 Symbol and DC1 and V C SSQ DC2 pins are connected in chip. DDQ pins are connected in chip. SSQ - 13 - 128M DDR SDRAM = 0 to 65qC) A Unit V DDQ 1.5 V 1.0 V/ns -0.4 V REF V REF =0.5*V tt DDQ R =50 REF =0 ...

Page 14

... DDR SDRAM -36 Max Min ...

Page 15

... X=A frequency dependent timing allowance account for tDQSQmax tQH Timing (CL4, BL2 CK DQS DQ COMMAND READA * VDD / VDDQ=2. 128M DDR SDRAM tHP 4 5 tDQSQ(max) tQH tDQSQ(max) Qa0 Qa1 Rev. 2.0 (Jan. 2003) ...

Page 16

... DAL + Precharge Exit self refresh to read com- t XSR t Power down exit time PDEX t Refresh interval time REF Note : 1. For normal write operation, even numbers of Din are to be written inside DRAM AC CHARACTERISTICS (II) K4D26323RA-GC2A Frequency Cas Latency 350MHz ( 2.86ns ) 4 300MHz ( 3.3ns ) 4 275MHz ( 3.6ns ) 4 ...

Page 17

... PRECH ACTIVEA ACTIVEB WRITEA tRP tRRD Multi Bank Interleaving Write Burst (@ BL= 128M DDR SDRAM ...

Page 18

... K4D26323RA-GC PACKAGE DIMENSIONS (144-Ball FBGA) 0.10 Max 0.45 ± 0.05 0.35 1.40 * VDD / VDDQ=2. INDEX MARK 12.0 <Top View> 0.8x11=8.8 0 ± 0.05 0.40 Max <Bottom View> 128M DDR SDRAM 12.0 A1 INDEX MARK 0.8 0.40 Unit : mm Rev. 2.0 (Jan. 2003) ...