saa4955tj NXP Semiconductors, saa4955tj Datasheet

saa4955tj

Related parts for saa4955tj

saa4955tj Summary of contents

Page 1

... DATA SHEET SAA4955TJ 2.9-Mbit field memory Product specification Supersedes data of 1997 Sep 25 File under Integrated Circuits, IC02 INTEGRATED CIRCUITS 1999 Apr 29 ...

Page 2

... SAA4955TJs can be cascaded to provide greater storage depth or a longer delay, without the need for additional circuitry. The SAA4955TJ contains separate 12-bit wide serial ports for reading and writing. The ports are controlled and clocked separately, so asynchronous read and write operations are supported. Independent read and write clock rates are possible ...

Page 3

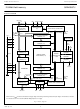

... OE internal 3 INPUT BUFFER ( SRCK OE RSTR and V ) require a 3.3 V supply. DD(O) Fig.1 Block diagram. 3 Product specification SAA4955TJ IE internal SERIAL WRITE CONTROLLER write write load write control acknowledge block address CLOCK 1) OSCILLATOR refresh clock D0 internal 1) WRITE ADDRESS COUNTER MEMORY ...

Page 4

... Product specification SAA4955TJ ...

Page 5

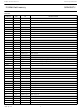

... SWCK 15 16 RSTW DD(P) 20 MGK675 Fig.2 Pin configuration. 1999 Apr 29 GND P 40 GND Q11 37 Q10 SRCK 25 RSTR DD( DD( Product specification SAA4955TJ ...

Page 6

... RSTW needs to stay LOW for a single SWCK cycle before another reset write operation can take place. If RSTW is HIGH for 1024 SWCK write clock cycles while WE is HIGH, the SAA4955TJ will enter a built-in test mode and will not be in regular operation. R ANDOM WRITE BLOCK ACCESS MODE ...

Page 7

... R ANDOM READ BLOCK ACCESS MODE The SAA4955TJ will enter random read block access mode if the following signal sequence is applied to control inputs RE and OE during the first four SRCK read clock cycles after a reset read (see Fig.12): ...

Page 8

... This means that if a reset read operation begins within 20 SWCK clock cycles after a reset write operation, the internal buffering of the SAA4955TJ will ensure that old + 0 5.0 V data will be read out (see Fig.16). New data will be read if the read pointer is delayed by 40 pointer positions or more after the write pointer ...

Page 9

... THERMAL CHARACTERISTICS SYMBOL R thermal resistance from junction to ambient th(j-a) 1999 Apr 29 continuously for 1024 SWCK clock cycles, the SAA4955TJ will enter test mode. It will exit test mode LOW for a single SWCK cycle or if RSTW is LOW for 2 SWCK clock cycles. CONDITIONS DD(P) ...

Page 10

... MHz see Fig.3 see Fig.3 see Fig.3 see Fig.3 see Fig.3 see Fig.3 see Fig.7 see Fig.7 see Fig.7 see Fig.8 see Fig.8 see Fig.8 see Fig.3 10 Product specification SAA4955TJ (1) MIN. TYP. MAX. 3.0 3.3 3.6 V 3.0 3.3 5 ...

Page 11

... SWCK. They are valid for the IL and the rising edge of SRCK. They are valid for the IL and V ). The load on each output capacitor to ground Product specification SAA4955TJ (1) MIN. TYP. MAX ...

Page 12

... Fig.4 Write cycle timing diagram (reset write with WE LOW). 1999 Apr h(RSTW) t su(RSTW) t h(RSTW Fig.3 Write cycle timing diagram (reset write). N disable N 12 Product specification SAA4955TJ su(RSTW) t su( MGK677 disable ...

Page 13

... Fig.6 IE controlled entry sequence of random write block access mode. 1999 Apr 29 serial input of write block address (13 SWCK) 17 random write block address LSB serial input of write block address (13 SWCK) 17 random write block address LSB 13 Product specification SAA4955TJ write latency write data (minimum 18 SWCK write data ...

Page 14

... Fig.8 Write cycle timing diagram (input enable = write mask operation). 1999 Apr 29 N disable t h(WE) t w(WEL) t h(D) N Fig.7 Write cycle timing diagram (write enable). disable N t h(IE) t w(IEL Product specification SAA4955TJ disable h(WE) t su(WE ...

Page 15

... Apr new old high Fig.9 Write mask operation. 15 Product specification SAA4955TJ old new new new MGK683 ...

Page 16

... Fig.11 Read cycle timing diagram (reset read with RE LOW). 1999 Apr h(RSTR) t su(RSTR) t h(RSTR Fig.10 Read cycle timing diagram (reset read Product specification SAA4955TJ su(RSTR ...

Page 17

... RSTR 1999 Apr 29 serial input of read block address (13 SRCK) random read block address h(RE) t w(REL) N Fig.13 Read cycle timing diagram (read enable). 17 Product specification SAA4955TJ read latency read data (minimum 20 SRCK LSB at block address: read data ...

Page 18

... SRCK t su(OE Q11 RSTR Fig.14 Read cycle timing diagram (output enable). 1999 Apr 29 disable disable t h(OE) t w(OEL) t dis(Q) high Product specification SAA4955TJ h(OE) t su(OE ACC t en( ...

Page 19

... Q1 to Q11 1999 Apr new new new minimum number of SWCK cycles delay to get new data Fig.15 New data access. 19 Product specification SAA4955TJ new new new ...

Page 20

... Q1 to Q11 1999 Apr new new new maximum number of SWCK cycles delay to get old data Fig.16 Old data access. 20 Product specification SAA4955TJ new new new ...

Page 21

... Fig.18 Cascade operation (timing waveforms). 21 Product specification SAA4955TJ RSTR 16 25 SRCK 15 26 SAA4955TJ Q0 to Q11 outputs MGK691 new new new old ...

Page 22

... VERSION IEC SOT449-1 1999 Apr scale (1) ( 0.51 0.81 0.32 26.2 10.3 1.27 0.38 0.66 0.18 25.9 10.0 REFERENCES JEDEC EIAJ MS027 22 Product specification SAA4955TJ detail 11.30 1.4 9.4 0.18 0.18 11.05 1.1 EUROPEAN ...

Page 23

... Use a low voltage ( less) soldering iron applied to the flat part of the lead. Contact time must be limited to 10 seconds 300 C. When using a dedicated tool, all other leads can be soldered in one operation within seconds between 270 and 320 C. 23 Product specification SAA4955TJ ...

Page 24

... Philips for any damages resulting from such improper use or sale. 1999 Apr 29 SOLDERING METHOD WAVE not suitable (2) suitable (3)(4) not recommended (5) not recommended 24 Product specification SAA4955TJ (1) REFLOW suitable suitable suitable suitable suitable ...

Page 25

... Philips Semiconductors 2.9-Mbit field memory 1999 Apr 29 NOTES 25 Product specification SAA4955TJ ...

Page 26

... Philips Semiconductors 2.9-Mbit field memory 1999 Apr 29 NOTES 26 Product specification SAA4955TJ ...

Page 27

... Philips Semiconductors 2.9-Mbit field memory 1999 Apr 29 NOTES 27 Product specification SAA4955TJ ...

Page 28

Philips Semiconductors – a worldwide company Argentina: see South America Australia: 34 Waterloo Road, NORTH RYDE, NSW 2113, Tel. +61 2 9805 4455, Fax. +61 2 9805 4466 Austria: Computerstr. 6, A-1101 WIEN, P.O. Box 213, Tel. + ...