54ls114 National Semiconductor Corporation, 54ls114 Datasheet

54ls114

Manufacturer Part Number

54ls114

Description

Dual Jk Negative Edge-triggered Flip-flop With Common Clocks And Clears

Manufacturer

National Semiconductor Corporation

Datasheet

1.54LS114.pdf

(6 pages)

C 1995 National Semiconductor Corporation

54LS114

Dual JK Negative Edge-Triggered

Flip-Flop with Common Clocks and Clears

General Description

The ’LS114 features individual J K and set inputs and com-

mon clock and common clear inputs When the clock goes

HIGH the inputs are enabled and data will be accepted The

logic level of the J and K inputs may be allowed to change

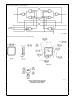

Connection Diagram

See NS Package Number E20A J14A or W14B

54LS114FMQB or 54LS114LMQB

Order Number 54LS114DMQB

Dual-In-Line Package

TL F 10176

J1 J2 K1 K2

CP

CD

SD1 SD2

Q1 Q2 Q1 Q2

Pin Names

TL F 10176 – 1

Data Inputs

Clock Pulse Input (Active Falling Edge)

Direct Clear Input (Active LOW)

Direct Set Inputs (Active LOW)

Outputs

when the Clock Pulse is HIGH and the bistable will perform

according to the truth table as long as the minimum setup

times are observed Input data is transferred to the outputs

on the negative-going edge of the clock pulse

Logic Symbol

Description

V

GND

CC

e

e

Pin 14

Pin 7

RRD-B30M105 Printed in U S A

TL F 10176 – 2

June 1989