54ls113 National Semiconductor Corporation, 54ls113 Datasheet

54ls113

Available stocks

Related parts for 54ls113

54ls113 Summary of contents

Page 1

... Dual JK Edge-Triggered Flip-Flop General Description The 54LS113 offers individual J K Set and Clock inputs When the clock goes HIGH the inputs are enabled and data may be entered The logic level of the J and K inputs may be changed when the clock pulse is HIGH and the bistable ...

Page 2

... Characteristics’’ 7V table are not guaranteed at the absolute maximum ratings 5 5V The ‘‘Recommended Operating Conditions’’ table will define the conditions for actual operation 125 C a 150 C a 54LS113 Min Nom ...

Page 3

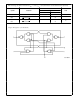

... Propagation Delay PLH PHL Dn n Logic Diagram (one half shown (See Section 1 for test waveforms and output load 54LS113 Min Units Max MHz 10205 – 3 ...

Page 4

4 ...

Page 5

... Physical Dimensions inches (millimeters) Ceramic Leadless Chip Carrier Package (E) 14-Lead Ceramic Dual-In-Line Package (J) Order Number 54LS113LMQB NS Package Number E20A Order Number 54LS113DMQB NS Package Number J14A 5 ...

Page 6

... Italiano National does not assume any responsibility for use of any circuitry described no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications Order Number 54LS113FMQB NS Package Number W14B 2 A critical component is any component of a life ...