hcts112ms Intersil Corporation, hcts112ms Datasheet

hcts112ms

Related parts for hcts112ms

hcts112ms Summary of contents

Page 1

... CP2N). The HCTS112MS utilizes advanced CMOS/SOS technology to achieve high-speed operation. This device is a member of radiation hardened, high-speed, CMOS/SOS Logic Family. The HCTS112MS is supplied lead Ceramic flatpack (K suffi SBDIP Package (D suffix). Ordering Information PART NUMBER ...

Page 2

... High Steady State Low Steady State Immaterial, = High-to-Low Transition * Output States Unpredictable if S and R Go High Simultaneously after Both being Low at the Same Time HCTS112MS TRUTH TABLE ...

Page 3

... VCC = 4.5V, VIH = 2.25V, Functional Test VIL = 0.8V (Note 2) NOTES: 1. All voltages referenced to device GND. 2. For functional tests, VO 4.0V is recognized as a logic “1”, and VO Specifications HCTS112MS Reliability Information Thermal Resistance SBDIP Package 10mA Ceramic Flatpack Package . . . . . . . . . . . 25mA Maximum Package Power Dissipation at +125 SBDIP Package ...

Page 4

... The parameters listed in Table 3 are controlled via design or process parameters. Min and Max Limits are guaranteed but not directly tested. These parameters are characterized upon initial design release and upon design changes which affect these characteristics. Specifications HCTS112MS GROUP (NOTES 1, 2) ...

Page 5

... AC measurements assume RL = 500 , CL = 50pF, Input 3ns, VIL = GND, VIH = 3V. 3. For functional tests VO 4.0V is recognized as a logic “1”, and VO TABLE 5. BURN-IN AND OPERATING LIFE TEST, DELTA PARAMETERS (+25 PARAMETER ICC IOL/IOH Specifications HCTS112MS (NOTES 1, 2) CONDITIONS TEMPERATURE 0.5V is recognized as a logic “0”. GROUP B SUBGROUP ...

Page 6

... Each pin except VCC and GND will have a resistor of 1K OPEN NOTE: Each pin except VCC and GND will have a resistor of 47K Group E, Subgroup 2, sample size is 4 dice/wafer 0 failures. Specifications HCTS112MS TABLE 6. APPLICABLE SUBGROUPS METHOD GROUP A SUBGROUPS 100%/5004 ...

Page 7

... Variables Data (All Delta operations). Data is identified by serial number. Data header includes lot number and date of test. • The Certificate of Conformance is a part of the shipping invoice and is not part of the Data Book. The Certificate of Conformance is signed by an authorized Quality Representative. HCTS112MS 100% Interim Electrical Test 1 (T1) 100% Delta Calculation (T0-T1) 100% Static Burn-In 2, Condition hrs ...

Page 8

... Positive Edge Trigger INPUT TW VIH VS VIL TH TSU TW INPUT CP VIH VS VIL TH = HOLD TIME TSU = SETUP TIME TW = PULSE WIDTH AC Load Circuit DUT 50pF RL = 500 HCTS112MS PARAMETER VCC VIH TPHL VS VIL TTHL GND 80% 20% PARAMETER VCC VIH VS VIL GND TEST POINT 497 AC VOLTAGE LEVELS HCTS UNITS 4 ...

Page 9

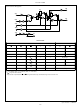

... Metallization Mask Layout J1 (3) S1 (4) Q1 (5) Q1 (6) Q2 (7) NOTE: The die diagram is a generic plot from a similar HCS device intended to indicate approximate die size and bond pad location. The mask series for the HCTS112 is TA14441A. HCTS112MS HCTS112MS K1 CP1 VCC (2) (1) (16) (8) (9) ...

Page 10

... For information regarding Intersil Corporation and its products, see web site http://www.intersil.com Sales Office Headquarters NORTH AMERICA Intersil Corporation P. O. Box 883, Mail Stop 53-204 Melbourne, FL 32902 TEL: (321) 727-9207 FAX: (321) 724-7240 HCTS112MS EUROPE Intersil SA Mercure Center 100, Rue de la Fusee 1130 Brussels, Belgium TEL: (32) 2.724.2111 FAX: (32) 2.724.22.05 ...