lc72134m Sanyo Semiconductor Corporation, lc72134m Datasheet

lc72134m

Related parts for lc72134m

lc72134m Summary of contents

Page 1

... Ordering number : EN5814 Overview The LC72134M is a dual PLL frequency synthesizer product that integrates on a single chip both an AM/FM audio broadcast reception PLL circuit (main PLL) and a dedicated FM multiplex reception PLL circuit (sub PLL). Since the main PLL circuit is equivalent to the LC72135M, software developed for that product can be used with this chip ...

Page 2

... Pin Assignments LC72134M No. 5814-2/27 ...

Page 3

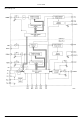

... Block Diagram LC72134M No. 5814-3/27 ...

Page 4

... However, since the oscillator circuit characteristics depend on the printed circuit board, circuit constants, and other factors, consult with the manufacturer of the crystal element. Electrical Characteristics in the Allowable Operating Ranges Parameter Internal feedback resistance Internal pull-down resistance Hysteresis Output high-level voltage LC72134M = Symbol Conditions V max V ...

Page 5

... FMINa 18 the swallow counter. signal input • The divisor can be set to a value in the range 272 to 65535. Since the internal divide-by-two prescaler is used, the actual divisor will be twice the set value. LC72134M Symbol Conditions V 1 PDa, PDb ...

Page 6

... Clock output (DO). • Output for serial data transmitted to the controller. The content of the data DO 5 Output data transmitted is determined by DOC0 through DOC2. • LC72134M power supply ( Power supply DD • The power on reset circuit operates when power is first applied Ground • ...

Page 7

... This pin goes to the high-impedance state when the frequencies match. Sub PLL low- AINb 10 pass filter • Connections for the n-channel MOS transistor used for the sub PLL active low- amplifier pass filter. AOUTb 9 transistor LC72134M Function Equivalent circuit No. 5814-7/27 ...

Page 8

... IN2 (92 IN3 (B2 OUT (A2 LC72134M Address • Control data input (serial data input) mode • 24 bits of data are input • See the “DI Control Data (serial data input)” section for details on the content of the input data. • ...

Page 9

... Structure of the DI Control Data (serial data input) • IN1 (Main PLL/Latch- • IN2 (Main PLL/Latch-a) • IN3 (Sub PLL/Latch-b) LC72134M No. 5814-9/27 ...

Page 10

... The crystal oscillator circuit is stopped. Therefore applications must not select this mode while the sub PLL is operating. XS • Crystal oscillator element selection data 4.5 MHz 7.2 MHz Note that 7.2 MHz is selected after a power on reset. LC72134M Function (* : don’t care) SNS LSB Set divisor (N) Actual divisor ...

Page 11

... Determines the output state of the BO1 through BO4 and IO2 output ports. Output port data Data = 0: Open 5 BO1 to BO4 Data = 1: Low level IO2 • The data is reset to 0, setting the pins to the open state, after a power on reset. LC72134M Function GT0 Measurement time Wait time ...

Page 12

... Dead zone width: DZA < DZB < DZC < DZD Clock time base • Setting the TBC bit to 1 causes an 8-Hz clock time base signal with a 40% duty to be output from the 9 BO1 pin. (The BO1 data will be ignored.) TBC LC72134M Function DOC1 DOC0 DO pin state 0 ...

Page 13

... ULb Unlocked state detection output 0 17 switching data 0 ULa, ULb 1 1 LC72134M Function Normal operation Forced to low All these bits must be set to 0. Operating state Input pin frequency range The FMINb counter operates The FMINb counter is stopped 10 to 160 MHz (FMINb is pulled down) ...

Page 14

... Data that reflects the LCTS bit in the serial input data. The LCT output data allows applications to verify the IF counter selection IF counter input pin selection (IFIN1 or IFIN2). data 4 LCT = 0: IFIN1 selected. LCT LCT = 1: IFIN2/I1 selected. Serial Data Input (IN1/IN2/IN3) t • CL: Normal (high) LC72134M Description ≥ 0.75 µ ...

Page 15

... CL: Normal (low) Serial Data Output (Out • CL: Normal (high) • CL: Normal (low) Note: The data conversion times (t and n-channel open-drain circuit. LC72134M ≥ 0.75 µ < 0.35 µ depend on the value of the pull-up resistor and the printed circuit board capacitance since the DO pin ...

Page 16

... Data output time t DO LC72134M When CL is stopped at the low level When CL is stopped at the high level Conditions These values differ depending on the value of the pull-up resistor used and the printed circuit board capacitance Ratings Unit min ...

Page 17

... For MW with a step size of 10 kHz (DVS = 0, SNS = 0: AMIN low-speed operation selected 1000 kHz (IF = +450 kHz) WM VCO = 1450 kHz Main PLL fref = 10 kHz ( 1450 kHz (MW VCO) 10 kHz (fref) = 145 LC72134M Set divisor Actual divisor 272 to 65535 Twice the set value ...

Page 18

... For FM with a step size of 50 kHz (SDVS = 1: FMINb operating 90.0 MHz (IF = +10.7 MHz) FM VCO = 100.7 MHz Sub PLL fref = 25 kHz (RS0 = 1, RS1 = 0) 100.7 MHz (FM VCO) 25 kHz (fref) 2 (for the FMINb 1/2 prescaler) = 2014 LC72134M Set divisor Actual divisor: N Input frequency range 272 to 8191 Twice the set value — ...

Page 19

... Structure of the IF Counter The LC72134M IF counter is a 20-bit binary counter, and takes the IF signal from the IFIN1 or IFIN2/I1 pin as its input. The result of the count can be read out serially MSB first from the DO pin. Measurement time GT1 GT0 Measurement time (GT) ...

Page 20

... For example, if fref is 1 kHz (a period of 1 ms) applications must wait at least 2 ms after the divisor N is changed before performing a locked/unlocked check. LC72134M Figure 1 Unlocked State Detection Timing No. 5814-20/27 ...

Page 21

... LC72134M Figure 2 Circuit Structure Figure 3 Combining with Software No. 5814-21/27 ...

Page 22

... Outputting the unlocked state data in the serial data In the LC72134M, the unlocked state data (UL), once set to the unlocked state, is not reset unless data is output (or input). At the point of data output (1) in figure 3, the VCO frequency will be stable (locked), but since the divisor N was changed and a data output operation has not yet been performed, the unlocked state data will indicate the unlocked state ...

Page 23

... FM reception, or where it is desirable to increase the pilot margin in AM stereo reception. However, if such a high signal-to-noise ratio is not required for FM reception adequate pilot margin can be acquired in AM stereo reception stereo is not required, then either DZC or DZD, in which there is a dead band, should be chosen. LC72134M ≥ Charge pump Dead band ON/ON – ...

Page 24

... It is also possible to have the DO pin reflect the state of an input pin to input that state to the microcontroller. • Power supply pins A capacitor of at least 2000 pF must be inserted between the power supply V capacitor must be placed as close as possible to the V LC72134M and and V pins ...

Page 25

... Pin States after a Power on Reset LC72134M No. 5814-25/27 ...

Page 26

... Sample Application Circuits FM/AM Tuner + FM Tuner (for FM Subcarrier) Note: Since the areas enclosed in dotted lines ( Therefore, lines in the printed circuit board pattern should be made as short as possible and these areas should be surrounded by the ground pattern. LC72134M ) are high-impedance circuits, they are susceptible to noise. No. 5814-26/27 ...

Page 27

... SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties. This catalog provides information as of March, 1998. Specifications and information herein are subject to change without notice. LC72134M ) are high-impedance circuits, they are susceptible to noise. PS No. 5814-27/27 ...