UPD4701AGT NEC [NEC], UPD4701AGT Datasheet - Page 3

UPD4701AGT

Manufacturer Part Number

UPD4701AGT

Description

MOS INTEGRATED CIRCUIT

Manufacturer

NEC [NEC]

Datasheet

1.UPD4701AGT.pdf

(16 pages)

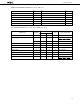

PIN FUNCTIONS

CPU

interface

block

Mouse

interface

block

Power

supply

block

Pin Name

RESET X

RESET Y

MIDDLE

RIGHT

X

Y

D

LEFT

X/Y

U/L

V

A

A

V

CS

CF

SF

0 to 7

, X

, Y

DD

SS

B

B

(Schmitt input)

(Schmitt input)

(Schmitt input)

Input/Output

(3-state)

Output

Output

Output

Input

Input

Input

Input

Input

Input

Input

Chip Select input. “L” input activates outputs D0 to 7.

“H” input sets outputs D0 to 7 to high impedance.

Output data is latched on the fall edge of CS. “L” must be maintained during a

count data read.

Counter Select input. “L” input selects the X counter, and “H” input selects the

Y counter.

Byte Select input. “L” input selects the lower byte and “H” input selects the

upper byte, controlling data output.

Counter reset inputs. RESET X input resets the X counter, and RESET Y input

resets the Y counter. Both are active-“H”.

Bus for data output to the CPU. Outputs the byte data selected by the X/Y and

U/L inputs.

The data latched on the fall of CS is output.

Counter flag output. Set (= “L” output) when the X or Y counter changes while

CS = “H”. Reset (= “H” output) on the fall of CS. While CS = “L”, count flag

output is disabled and the “H” level is output.

Switch flag output. Becomes active (= “L” output) when the RIGHT, LEFT or

MIDDLE switch input is “L”.

X counter 2-phase signal input pins

Y counter 2-phase signal input pins

Key switch input pins. Key switch input are read as the high-order 4 bits of the

X counter and Y counter upper byte as the internal status.

+5 V power supply connection pin

Ground pin

SF

Upper Byte

Key Input Status

L

R

M

Function

C

11

Count Data

C

10

C

9

C

8

PD4701A

3