IDT71215 Integrated Device Technology, IDT71215 Datasheet

IDT71215

Available stocks

Related parts for IDT71215

IDT71215 Summary of contents

Page 1

... Match and Read operations are both asynchronous in order to provide the fastest access times possible, while Write operations are synchronous for ease of system timing. The IDT71215 uses a 5V power supply on Vcc with sepa- rate V CCQ with both 5.0V TTL and 3.3V LVTTL Logic levels. The ...

Page 2

... IDT71215 BiCMOS 16Kx15 CACHE-TAG RAM PIN CONFIGURATION DTY / COMMERCIAL TEMPERATURE RANGE PN80-1 TQFP TOP VIEW 14 TAG8 TAG7 TAG6 VLD / S1 OUT ...

Page 3

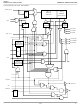

... IDT71215 BiCMOS 16Kx15 CACHE-TAG RAM FUNCTIONAL BLOCK DIAGRAM ADDR (0:13) CS1 CS2 Reg TAG (0:11) OET WRITE (pos) PULSE GENERATOR WET Reg WES CLK RESET (neg) PULSE GENERATOR RESET PWRDN SFUNC W/ R BRDYH BRDYIN Reg BRDYOE 0 Reg MEMORY 1 TAG BITS Data in Register 14.3 COMMERCIAL TEMPERATURE RANGE ...

Page 4

... IDT71215 BiCMOS 16Kx15 CACHE-TAG RAM TRUTH TABLES CHIP SELECT, RESET, AND POWER-DOWN FUNCTIONS CS2 CLK CS1 RESET PWRDN RESET WET WET WES CS1 PWRDN CHIP SELECT FUNCTION RESET FUNCTION ...

Page 5

... IDT71215 BiCMOS 16Kx15 CACHE-TAG RAM TRUTH TABLES (CONT.) ( MATCH FUNCTION CS2 SFUNC CS1 OET WET WES CS1 OET WET WES ...

Page 6

... IDT71215 BiCMOS 16Kx15 CACHE-TAG RAM RECOMMENDED DC OPERATING CONDITIONS Symbol Parameter Min. V Supply Voltage 4. Output Buffers 4.75 CCQ V 3.3V Output Buffers 3.0 CCQ V Supply Ground Input High Voltage 2 I/O High Voltage 2.2 IHQ V Input Low Voltage –0.5 IL NOTE (min.) = –1.5V for pulse width of less than 10ns, once per cycle. ...

Page 7

... IDT71215S9 IDT71215S10 IDT71215S12 Max. Min. Max. Min. 4 — 4 — — 1 — 1 — 60 — 60 — 2 — 2 — 2 — 10 — 10 — — 120 — ...

Page 8

... IDT71215S8 IDT71215S9 Min. Max. 15 4.5 4 Invalid — BRDY 1.5 — — 0 LOW 5 Active 50 WES 14.3 COMMERCIAL TEMPERATURE RANGE IDT71215S10 IDT71215S12 Min. Max. Min. Max. Min. — 15 — 15 — 16.6 — 4.5 — 4.5 — 5 — 4.5 — 4.5 — 5 — 3 — 3 — 3 — ...

Page 9

... BRDY Valid — 6 BRDY Invalid — 6 Valid — 7 BRDY — 6 — 6 Invalid — 7 BRDY Valid — 8 BRDY 14.3 COMMERCIAL TEMPERATURE RANGE IDT71215S9 IDT71215S10 IDT71215S12 Min. Max. Min. Max. Min. — 9 — 10 — — 9 — 10 — — 9 — 10 — 1 — 1 — ...

Page 10

... IDT71215 BiCMOS 16Kx15 CACHE-TAG RAM AC TEST CONDITIONS Input Pulse Levels Input Rise/Fall Times Input Timing Reference Levels Output Timing Reference Levels AC Test Load AC TEST LOADS V CCQ Outputs 347 Figure 1. AC Test Load Tag I/O and Outputs 347 Figure 3. AC Test Load (for t ...

Page 11

... IDT71215 BiCMOS 16Kx15 CACHE-TAG RAM TIMING WAVEFORMS OF WRITE AND READ CYCLES COMMERCIAL TEMPERATURE RANGE 14.3 11 ...

Page 12

... IDT71215 BiCMOS 16Kx15 CACHE-TAG RAM TIMING WAVEFORMS OF MATCH AND FUNCTIONS BRDY BRDY 14.3 COMMERCIAL TEMPERATURE RANGE 12 ...

Page 13

... IDT71215 BiCMOS 16Kx15 CACHE-TAG RAM TIMING WAVEFORMS OF RESET RESET CLK t SR RESET t PDSR PWRDN VLD OUT DTY OUT WT OUT t S WES WET BRDY MATCH TAG (0:11) NOTE: 1. Transition is measured 200mV from steady state. CLOCK TIMING WAVEFORM t CH CLK 2.0V 2.0V TIMING WAVEFORMS OF BRDY BRDY ...

Page 14

... IDT71215 BiCMOS 16Kx15 CACHE-TAG RAM TIMING WAVEFORMS OF OES OES OES VLD OUT DTY OUT Valid Output WT OUT NOTE: 1. Transition is measured 200mV from steady state. TIMING WAVEFORMS OF POWER DOWN FUNCTION PWRDN t WHPL CLK t RHPL RESET WET WES TAG (0:11) VLD OUT DTY ...