MC68HC711G5 MOTOROLA [Motorola, Inc], MC68HC711G5 Datasheet - Page 61

MC68HC711G5

Manufacturer Part Number

MC68HC711G5

Description

High-density Complementary Metal Oxide Semiconductor (HCMOS) Microcontroller

Manufacturer

MOTOROLA [Motorola, Inc]

Datasheet

1.MC68HC711G5.pdf

(195 pages)

- Current page: 61 of 195

- Download datasheet (824Kb)

MC68HC11G5

5.2.5

On reset, both the X bit and the I bit in the CCR are set to inhibit all maskable interrupts and XIRQ.

After minimum system initialization, software may clear the X bit by a TAP instruction, thus enabling

XIRQ interrupts. Thereafter, software cannot set the X bit. Thus, an XIRQ is effectively a non-

maskable interrupt. Since the operation of the I bit related interrupt structure has no effect on the

X bit, the internal XIRQ pin remains effectively non-masked. In the interrupt priority logic, the XIRQ

interrupt is a higher priority than any source that is maskable by the I bit. All I bit related interrupts

operate normally with their own priority relationships.

When an I bit related interrupt occurs, the I bit is automatically set by hardware after stacking the

CCR byte. The X bit is not affected. When an X bit related interrupt occurs, both the X and the I bit

are automatically set by hardware after stacking the CCR byte. A return from interrupt (RTI)

instruction restores the X and I bits to their pre-interrupt request state.

5.2.6

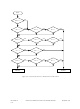

Interrupts obey a fixed hardware priority circuit to resolve simultaneous requests. However, one I bit

related interrupt source may be elevated to the highest I bit priority position in the resolution circuit.

Six interrupt sources are not masked by the I bit in the condition codes register and have the fixed

priority relationship:

1.

2.

3.

4.

5.

6.

SWI is actually an instruction and has highest priority other than reset in the sense that once the SWI

opcode is fetched, no other interrupt can be honoured until after the first instruction in the SWI

service routine has been executed. The scenario is similar for the illegal opcode.

Each of these sources is an input to the priority resolution circuit. The highest I bit masked priority

input to the resolution circuit is assigned under software control (via the HPRIO register) to be

connected to any one of the remaining I bit related interrupt sources. In order to avoid timing races

the HPRIO register may only be written while the I bit related interrupts are inhibited (I bit in CCR

set). An interrupt which is assigned to this high priority position is still subject to masking by any

associated control bits or by the I bit in the CCR. The address from which the interrupt vector is

fetched is not affected by assigning a source to this higher priority position.

Reset

Clock failure monitor

COP failure

Illegal opcode

SWI

XIRQ

Interrupt Mask Bits in Condition Code Register

Priority and Masking Structure

RESETS, INTERRUPTS AND LOW POWER MODES

MOTOROLA

5-9

Related parts for MC68HC711G5

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Motorola, Inc [VOLTAGE REGULATOR]

Manufacturer:

Motorola

Datasheet:

Part Number:

Description:

6367254 MOTOROLA SC (XSTRS/R F)

Manufacturer:

MOTOROLA [Motorola, Inc]

Datasheet:

Part Number:

Description:

MC1494LMotorola, Inc [MONOLITHIC FOUR-QUADRANT MULTIPLIER]

Manufacturer:

Motorola

Datasheet:

Part Number:

Description:

MC1466LMotorola, Inc [PRECISION WIDE RANGE VOLTAGE AND CURRENT REGULATOR]

Manufacturer:

Motorola

Datasheet:

Part Number:

Description:

MC145532DWMotorola, Inc [ADPCM Transcoder]

Manufacturer:

Motorola

Datasheet:

Part Number:

Description:

Silicon Controlled Rectifiers

Manufacturer:

MOTOROLA [Motorola, Inc]

Datasheet:

Part Number:

Description:

RF Power Field Effect Transistors N-Channel Enhancement-Mode Lateral MOSFETs

Manufacturer:

MOTOROLA [Motorola, Inc]

Datasheet:

Part Number:

Description:

RF POWER FIELD EFFECT TRANSISTORS

Manufacturer:

MOTOROLA [Motorola, Inc]

Datasheet:

Part Number:

Description:

LATERAL N-CHANNEL BROADBAND RF POWER MOSFETs

Manufacturer:

MOTOROLA [Motorola, Inc]

Datasheet:

Part Number:

Description:

RF POWER FIELD EFFECT TRANSISTOR

Manufacturer:

MOTOROLA [Motorola, Inc]

Datasheet:

Part Number:

Description:

RF LOW POWER TRANSISTOR NPN SILICON

Manufacturer:

MOTOROLA [Motorola, Inc]

Datasheet:

Part Number:

Description:

PLASTIC SURFACE MOUNT ZENER DIODES 1.5 WATTS 3.3-68 VOLTS

Manufacturer:

MOTOROLA [Motorola, Inc]

Datasheet:

Part Number:

Description:

OVERVOLTAGE TRANSIENT SUPPRESSOR

Manufacturer:

MOTOROLA [Motorola, Inc]

Datasheet:

Part Number:

Description:

TMOS POWER FET 15 AMPERES 60 VOLTS

Manufacturer:

MOTOROLA [Motorola, Inc]

Datasheet:

Part Number:

Description:

TMOS POWER FET LOGIC LEVEL 19 AMPERES 30 VOLTS RDS(on) = 0.099 OHM

Manufacturer:

MOTOROLA [Motorola, Inc]

Datasheet: