NCP1392B_09 ONSEMI [ON Semiconductor], NCP1392B_09 Datasheet

NCP1392B_09

Related parts for NCP1392B_09

NCP1392B_09 Summary of contents

Page 1

NCP1392B, NCP1392D High-Voltage Half-Bridge Driver with Inbuilt Oscillator The NCP1392B self−oscillating high voltage MOSFET driver primarily tailored for the applications using half bridge topology. Due to its proprietary high−voltage technology, the driver accepts bulk voltages up to 600 ...

Page 2

Rbo1 AC OUTPUT + PFC FRONT STAGE Cbulk Rbo2 Rf PIN FUNCTION DESCRIPTION Pin # Pin Name Function 1 V Supplies the Driver Timing Resistor 3 BO Brown−Out 4 GND IC Ground 5 Mlower Low−Side Driver Output ...

Page 3

ref PFC Delay (100ms ref V DD PON V CC RESET V CC Management V CC Clamp TSD − 0.5ms + Filter + Vref EN − 20ms ...

Page 4

ref PFC Delay (12.6 ms ref V DD PON V CC RESET V CC Management V CC Clamp TSD BO + 20ms − Filter + Vref BO − SW ...

Page 5

MAXIMUM RATINGS TABLE Symbol Vbridge High Voltage Bridge Pin − Pin 6 Vboot − Floating Supply Voltage Vbridge VDRV_HI High−Side Output Voltage VDRV_LO Low−Side Output Voltage dVbridge/dt Allowable Output Slew Rate I Maximum Current that Can Flow into V CC ...

Page 6

ELECTRICAL CHARACTERISTICS (For typical values unless otherwise noted) CC Characteristic SUPPLY SECTION Turn−On Threshold Level, V Going Up CC Minimum Operating Voltage after Turn−On Startup Voltage on the Floating Section Cutoff Voltage on the Floating ...

Page 7

ELECTRICAL CHARACTERISTICS unless otherwise noted) CC Characteristic PROTECTION Brown Out discharge time (B Version) (Note 2) Brown Out discharge time (D Version) (Note 2) 2. Guaranteed by design. (For typical values T = 25°C, for min/max ...

Page 8

TEMPERATURE (°C) Figure 4. V CCon 8.85 8.80 8.75 8.70 8.65 8.60 8.55 −40 − TEMPERATURE (°C) Figure 6. ...

Page 9

TEMPERATURE (°C) Figure 10 Version) SWmax 25.05 25.00 24.95 24.90 24.85 24.80 24.75 −40 − TEMPERATURE (°C) Figure 12. ...

Page 10

TEMPERATURE (°C) Figure 16 Version) dead 109 108 107 106 105 104 103 102 101 100 90 −40 − TEMPERATURE ...

Page 11

TEMPERATURE (°C) Figure 22 discharge 19.4 19.2 19.0 18.8 18.6 18.4 18.2 18.0 17.8 17.6 17.4 −40 − ...

Page 12

The NCP1392 is primarily intended to drive low cost half bridge applications and especially resonant half bridge applications. The IC includes several features that help the designer to cope with resonant SPMS design. All features are described thereafter: • Wide ...

Page 13

This is valuable for applications that are supplied from auxiliary winding and V capacitor is supposed to provide CC energy during PFC delay period. For the resonant applications and light ballast applications it is necessary to adjust minimum operating frequency ...

Page 14

V bulk R upper BO R lower Figure 30. The internal Brown−Out Configuration with an Offset Current Sink A resistive divider made of R upper portion of the HV rail on Pin 3. Below the turn−on level, the 18.2 mA ...

Page 15

Figure 31. Simulation Results for 350/250 ON/OFF Brown−Out Levels The IBO current sink is turned ON for BOdisch time after any controller restart to let the BO input voltage stabilize (there can be connected big capacitor to the BO input ...

Page 16

Vbulk_ON Vbulk_OFF Vbulk 1 V VBO BO_OK Vcc DRV_EN Figure 33. BO Input Functionality −V Vbulk_ON Vbulk_OFF Vbulk 1 V VBO BO_OK Vcc DRV_EN Figure 34. BO Input Functionality − V PFCdelay < V < PFC Start Follows ...

Page 17

Vbulk_ON Vbulk_OFF Vbulk 1 V VBO BO_OK Vcc DRV_EN Figure 35. BO Input Functionality − V Non−Latched Enable Input (B Version only) The non−latched input stops output drivers immediately the BO terminal voltage grows above 2 V threshold. The enable ...

Page 18

The dimming feature can be easily aid to the ballast application by adding two bipolar transistors (Figure 14). Transistor Q2 pullup BO input when dimming signal is high fstart Voltage Feedback Figure 37. Skip ...

Page 19

Voltage Feedback IC1 TLV431 R4 Figure 39. Skip Mode Feature Implementation (Better Accuracy) Figures 37 and 39 shows skip implementation using NCP1392 driver. Voltage across resistor R1 (R4) increases when converter ...

Page 20

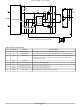

The High−Voltage Driver Figure 40 shows the internal architecture of the high−voltage section. The device incorporates an upper UVLO circuitry that makes sure enough V Pulse Trigger DEAD TIME B A from latch high if OK Figure 40. The Internal ...

Page 21

0.25 (0.010 −Y− −Z− 0.25 (0.010 *For additional information on our Pb−Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting ...