ATMEGA48PV_11 ATMEL [ATMEL Corporation], ATMEGA48PV_11 Datasheet

ATMEGA48PV_11

Related parts for ATMEGA48PV_11

ATMEGA48PV_11 Summary of contents

Page 1

Features • High Performance, Low Power Atmel • Advanced RISC Architecture – 131 Powerful Instructions – Most Single Clock Cycle Execution – General Purpose Working Registers – Fully Static Operation – MIPS Throughput at ...

Page 2

Pin Configurations Figure 1-1. Pinout ATmega48P/88P/168P TQFP Top View (PCINT19/OC2B/INT1) PD3 1 (PCINT20/XCK/T0) PD4 2 GND 3 VCC 4 GND 5 VCC 6 (PCINT6/XTAL1/TOSC1) PB6 7 (PCINT7/XTAL2/TOSC2) PB7 8 28 MLF Top View (PCINT19/OC2B/INT1) PD3 1 (PCINT20/XCK/T0) PD4 2 ...

Page 3

Pin Descriptions 1.1.1 VCC Digital supply voltage. 1.1.2 GND Ground. 1.1.3 Port B (PB7:0) XTAL1/XTAL2/TOSC1/TOSC2 Port 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port B output buffers have symmetrical drive ...

Page 4

The various special features of Port D are elaborated in 86. 1.1 the supply voltage pin for the A/D Converter, PC3:0, and ADC7:6. It should be externally CC connected to V through a low-pass filter. Note ...

Page 5

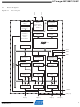

Block Diagram Figure 2-1. Block Diagram Watchdog Watchdog Oscillator Oscillator Circuits / Generation EEPROM 8bit T/C 0 8bit T/C 2 USART 0 PORT D (8) 8025MS–AVR–6/11 Power Timer Supervision POR / BOD & RESET Flash Clock 16bit T/C 1 ...

Page 6

The AVR core combines a rich instruction set with 32 general purpose working registers. All the 32 registers are directly connected to the Arithmetic Logic Unit (ALU), allowing two independent registers to be accessed in one single instruction executed in ...

Page 7

Comparison Between ATmega48P, ATmega88P and ATmega168P The ATmega48P, ATmega88P and ATmega168P differ only in memory sizes, boot loader sup- port, and interrupt vector sizes. sizes for the three devices. Table 2-1. Device ATmega48P ATmega88P ATmega168P ATmega88P and ATmega168P support ...

Page 8

... Resources A comprehensive set of development tools, application notes and datasheets are available for download on http://www.atmel.com/avr. Note: 4. Data Retention Reliability Qualification results show that the projected data retention failure rate is much less than 1 PPM over 20 years at 85°C or 100 years at 25°C. ...

Page 9

Register Summary Address Name Bit 7 (0xFF) Reserved – (0xFE) Reserved – (0xFD) Reserved – (0xFC) Reserved – (0xFB) Reserved – (0xFA) Reserved – (0xF9) Reserved – (0xF8) Reserved – (0xF7) Reserved – (0xF6) Reserved – (0xF5) Reserved – ...

Page 10

Address Name Bit 7 (0xC1) UCSR0B RXCIE0 (0xC0) UCSR0A RXC0 (0xBF) Reserved – (0xBE) Reserved – (0xBD) TWAMR TWAM6 (0xBC) TWCR TWINT (0xBB) TWDR (0xBA) TWAR TWA6 (0xB9) TWSR TWS7 (0xB8) TWBR (0xB7) Reserved – (0xB6) ASSR – (0xB5) Reserved ...

Page 11

Address Name Bit 7 (0x7F) DIDR1 – (0x7E) DIDR0 – (0x7D) Reserved – (0x7C) ADMUX REFS1 (0x7B) ADCSRB – (0x7A) ADCSRA ADEN (0x79) ADCH (0x78) ADCL (0x77) Reserved – (0x76) Reserved – (0x75) Reserved – (0x74) Reserved – (0x73) Reserved ...

Page 12

Address Name Bit 7 0x1D (0x3D) EIMSK – 0x1C (0x3C) EIFR – 0x1B (0x3B) PCIFR – 0x1A (0x3A) Reserved – 0x19 (0x39) Reserved – 0x18 (0x38) Reserved – 0x17 (0x37) TIFR2 – 0x16 (0x36) TIFR1 – 0x15 (0x35) TIFR0 – ...

Page 13

Instruction Set Summary Mnemonics Operands ARITHMETIC AND LOGIC INSTRUCTIONS ADD Rd, Rr Add two Registers ADC Rd, Rr Add with Carry two Registers ADIW Rdl,K Add Immediate to Word SUB Rd, Rr Subtract two Registers SUBI Rd, K Subtract ...

Page 14

Mnemonics Operands BRIE k Branch if Interrupt Enabled BRID k Branch if Interrupt Disabled BIT AND BIT-TEST INSTRUCTIONS SBI P,b Set Bit in I/O Register CBI P,b Clear Bit in I/O Register LSL Rd Logical Shift Left LSR Rd Logical ...

Page 15

Mnemonics Operands POP Rd Pop Register from Stack MCU CONTROL INSTRUCTIONS NOP No Operation SLEEP Sleep WDR Watchdog Reset BREAK Break Note: 1. These instructions are only available in ATmega168P. 8025MS–AVR–6/11 Description Rd ← STACK (see specific descr. for Sleep ...

Page 16

Ordering Information 9.1 ATmega48P Speed (MHz) Power Supply (V) (3) 10 1.8 - 5.5 (3) 20 2.7 - 5.5 Note: 1. This device can also be supplied in wafer form. Please contact your local Atmel sales office for detailed ...

Page 17

ATmega88P Speed (MHz) Power Supply (V) (3) 10 1.8 - 5.5 (3) 20 2.7 - 5.5 Note: 1. This device can also be supplied in wafer form. Please contact your local Atmel sales office for detailed ordering information and ...

Page 18

ATmega168P (3) Speed (MHz) Power Supply (V) 10 1.8 - 5.5 20 2.7 - 5.5 Note: 1. This device can also be supplied in wafer form. Please contact your local Atmel sales office for detailed ordering information and minimum ...

Page 19

Packaging Information 10.1 32A PIN 1 IDENTIFIER C Notes: 1. This package conforms to JEDEC reference MS-026, Variation ABA. 2. Dimensions D1 and E1 do not include mold protrusion. Allowable protrusion is 0.25 mm per side. Dimensions D1 and ...

Page 20

Pin TOP VIEW 0.20 b 0.4 Ref BOTTOM VIEW (4x) The terminal # Laser-marked Feature. Note: Package Drawing Contact: packagedrawings@atmel.com 8025MS–AVR–6/ ...

Page 21

Pin TOP VIEW Pin #1 Notch (0. BOTTOM VIEW Note: JEDEC Standard MO-220, Fig. 2 (Anvil Singulation), VHHD-2. 2325 Orchard Parkway San Jose, CA 95131 ...

Page 22

A SEATING PLANE Note: 1. Dimensions D and E1 do not include mold Flash or Protrusion. Mold Flash or Protrusion shall not exceed 0.25 mm (0.010"). 2325 Orchard Parkway San Jose, CA 95131 R 8025MS–AVR–6/11 ...

Page 23

Errata 11.1 Errata ATmega48P The revision letter in this section refers to the revision of the ATmega48P device. 11.1.1 Rev known errata. 11.1.2 Rev known errata. 11.1.3 Rev. A Not Sampled. 11.2 Errata ATmega88P The ...

Page 24

Datasheet Revision History Please note that the referring page numbers in this section are referred to this document. The referring revision in this section are referring to the document revision. 12.1 Rev. 8025M-06/ 12.2 Rev. 8025L-07/10 ...

Page 25

Rev. 8025G-01/ 10. 11. 12. 13. 14. 15. 12.8 Rev. 8025F-08/ 12.9 Rev. 8025E-08/ 10. 11. 12. 13. 14. ...

Page 26

Rev. 8025D-03/ 12.11 Rev. 8025C-01/08 1. 12.12 Rev. 8025B-01/ 10. 11. 12. 13. 14. 15. 12.13 Rev. 8025A-07/07 1. 8025MS–AVR–6/11 Updated figures in ”Speed Grades” on ...

Page 27

Atmel Corporation Atmel Asia Limited 2325 Orchard Parkway Unit 1-5 & 16, 19/F San Jose, CA 95131 BEA Tower, Millennium City 5 USA 418 Kwun Tong Road Tel: (+1)(408) 441-0311 Kwun Tong, Kowloon Fax: (+1)(408) 487-2600 HONG KONG www.atmel.com Tel: ...