AT89C52-12AC ATMEL Corporation, AT89C52-12AC Datasheet

AT89C52-12AC

Available stocks

Related parts for AT89C52-12AC

AT89C52-12AC Summary of contents

Page 1

... The on-chip Flash allows the program memory to be reprogrammed in-system conventional nonvolatile memory programmer. By combining a versatile 8-bit CPU with Flash on a monolithic chip, the Atmel AT89C52 is a powerful microcomputer which provides a highly flexible and cost effective solution to many embedded control applications ...

Page 2

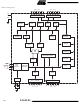

... Block Diagram V CC GND RAM ADDR. REGISTER B REGISTER PSEN TIMING ALE/PROG INSTRUCTION AND REGISTER CONTROL RST OSC AT89C52 4-62 P0.0 - P0.7 PORT 0 DRIVERS PORT 0 PORT 2 RAM LATCH LATCH ACC TMP2 TMP1 ALU INTERRUPT, SERIAL PORT, AND TIMER BLOCKS PSW PORT 1 LATCH PORT 1 DRIVERS P1 ...

Page 3

... Flash, 256 bytes of RAM, 32 I/O lines, three 16-bit timer/counters, a six-vector two-level interrupt architecture, a full duplex serial port, on-chip oscillator, and clock cir- cuitry. In addition, the AT89C52 is designed with static logic for operation down to zero frequency and supports two software selectable power saving modes. The Idle Mode stops the CPU while allowing the RAM, timer/counters, serial port, and interrupt system to continue functioning ...

Page 4

... PSEN Program Store Enable is the read strobe to external pro- gram memory. When the AT89C52 is executing code from external pro- gram memory, PSEN is activated twice each machine cycle, except that two PSEN activations are skipped during each access to external data memory. ...

Page 5

... When either RCLK or TCLK = 1, this bit is ignored and the timer is forced to auto-reload on Timer 2 overflow. Data Memory The AT89C52 implements 256 bytes of on-chip RAM. The upper 128 bytes occupy a parallel address space to the Special Function Registers. That means the upper 128 bytes have the same addresses as the SFR space but are physically separate from SFR space ...

Page 6

... Timer 0 and 1 Timer 0 and Timer 1 in the AT89C52 operate the same way as Timer 0 and Timer 1 in the AT89C51. Timer 2 Timer 16-bit Timer/Counter that can operate as either a timer or an event counter. The type of operation is selected by bit C/T2 in the SFR T2CON (shown in Table 2). ...

Page 7

Figure 2 shows Timer 2 automatically counting up when DCEN = 0. In this mode, two options are selected by bit EXEN2 in T2CON. If EXEN2 = 0, Timer 2 counts up to 0FFFFH and then sets the TF2 bit ...

Page 8

... C/ PIN Figure 4. Timer 2 in Baud Rate Generator Mode NOTE: OSC. FREQ. IS DIVIDED BY 2, NOT 12 ÷ 2 OSC C/ C/ PIN TRANSITION DETECTOR T2EX PIN AT89C52 4-68 (DOWN COUNTING RELOAD VALUE) 0FFH 0FFH OVERFLOW TH2 TL2 CONTROL TR2 RCAP2H RCAP2L (UP COUNTING RELOAD VALUE) TH2 ...

Page 9

Baud Rate Generator Timer 2 is selected as the baud rate generator by setting TCLK and/or RCLK in T2CON (Table 2). Note that the baud rates for transmit and receive can be different if Timer 2 is used for the ...

Page 10

... Note, however, that the baud-rate and clock-out frequencies cannot be determined independently from one another since they both use RCAP2H and RCAP2L. UART The UART in the AT89C52 operates the same way as the UART in the AT89C51. Interrupts The AT89C52 has a total of six interrupt vectors: two exter- nal interrupts (INT0 and INT1), three timer interrupts (Tim- ers 0, 1, and 2), and the serial port interrupt ...

Page 11

Oscillator Characteristics XTAL1 and XTAL2 are the input and output, respectively inverting amplifier that can be configured for use as an on-chip oscillator, as shown in Figure 7. Either a quartz crystal or ceramic resonator may be used. ...

Page 12

... Chip Erase Mode. Programming Algorithm: Before programming the AT89C52, the address, data and control signals should be set up according to the Flash programming mode table and Figures 9 and 10. To program the AT89C52, take the fol- lowing steps. 1. Input the desired memory location on the address lines. ...

Page 13

Chip Erase: The entire Flash array is erased electrically by using the proper combination of control signals and by holding ALE/PROG low for 10 ms. The code array is written with all 1s. The chip erase operation must be executed ...

Page 14

... Figure 10. Verifying the Flash Memory +5V V ADDR. CC OOOOH/1FFFH PGM P0 DATA ALE PROG SEE FLASH PROGRAMMING MODES TABLE 3-24 MHz RST V IH PSEN PP +5V AT89C52 PGM DATA P0 P2.0 - P2.4 (USE 10K A8 - A12 PULLUPS) P2.6 P2.7 ALE P3.6 P3.7 XTAL 2 EA XTAL1 RST GND PSEN Min Max Units 11 ...

Page 15

Flash Programming and Verification Waveforms - High Voltage Mode (V P1.0 - P1.7 P2.0 - P2.4 PORT 0 ALE/PROG EA/V PP P2.7 (ENABLE) P3.4 (RDY/BSY) Flash Programming and Verification Waveforms - Low Voltage Mode (V P1.0 - P1.7 P2.0 - ...

Page 16

... Port Ports Maximum total I for all output pins exceeds the test condition than the listed test conditions. 2. Minimum V for Power Down is 2V. CC AT89C52 4-76 *NOTICE: = -40°C to 85°C and Condition (Except EA) (Except XTAL1, RST) (XTAL1, RST ...

Page 17

AC Characteristics Under operating conditions, load capacitance for Port 0, ALE/PROG, and PSEN = 100 pF; load capacitance for all other outputs = 80 pF. External Program and Data Memory Characteristics Symbol Parameter 1/t Oscillator Frequency CLCL t ALE Pulse ...

Page 18

... External Program Memory Read Cycle t LHLL ALE t AVLL PSEN PORT 0 PORT 2 External Data Memory Read Cycle t LHLL ALE PSEN RD t AVLL PORT FROM RI OR DPL PORT 2 P2 A15 FROM DPH AT89C52 4-78 t LLIV t LLPL t PLIV t PLAZ t PXIZ t LLAX t PXIX INSTR IN t AVIV A8 - A15 ...

Page 19

External Data Memory Write Cycle t LHLL ALE PSEN WR t AVLL PORT FROM RI OR DPL PORT 2 P2 A15 FROM DPH External Clock Drive Waveforms t CHCX V - ...

Page 20

... V - 0. TEST POINTS 0 0.45V Note Inputs during testing are driven at V for a logic 1 and 0.45V for a logic 0. Timing mea- surements are made at V max. for a logic 0. AT89C52 4-80 = 5.0V 20% and Load Capacitance = 80 pF MHz Osc Min 1.0 700 ...

Page 21

... Ordering Information Speed Power (MHz) Supply 20% Ordering Code AT89C52-12AC AT89C52-12JC AT89C52-12PC AT89C52-12QC AT89C52-12AI AT89C52-12JI AT89C52-12PI AT89C52-12QI AT89C52-12AA AT89C52-12JA AT89C52-12PA AT89C52-12QA AT89C52-16AC AT89C52-16JC AT89C52-16PC AT89C52-16QC AT89C52-16AI AT89C52-16JI AT89C52-16PI AT89C52-16QI AT89C52-16AA AT89C52-16JA AT89C52-16PA AT89C52-16QA AT89C52-20AC AT89C52-20JC AT89C52-20PC AT89C52-20QC AT89C52-20AI ...

Page 22

... Lead, 0.600" Wide, Plastic Dual Inline Package (PDIP) 44Q 44 Lead, Plastic Gull Wing Quad Flatpack (PQFP) AT89C52 4-82 Ordering Code Package AT89C52-24AC 44A AT89C52-24JC 44J AT89C52-24PC 40P6 AT89C52-24QC 44Q AT89C52-24AI 44A AT89C52-24JI 44J AT89C52-24PI 40P6 AT89C52-24QI 44Q Package Type Operation Range Commercial ( Industrial (- ...