CDP1881C Intersil Corporation, CDP1881C Datasheet

CDP1881C

Available stocks

Related parts for CDP1881C

CDP1881C Summary of contents

Page 1

... D18.3 The CDP1881C, CDP1882 and CDP1882C are supplied in 20 lead and 18 lead packages, respectively. The CDP1881C is supplied only in a dual-in-line plastic pack- age (E suffix). The CDP1882 is supplied in dual-in-line, hermetic side-brazed ceramic (D suffix) and in plastic (E suffix) packages. ...

Page 2

... Terminal) SS CDP1882 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -0.5V to +11V CDP1881C and CDP1882C -0.5V to +7V Input Voltage Range, All Inputs . . . . . . . . . . . . . -0. Input Current, Any One Input CAUTION: Stresses above those listed in the “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and opera- tion of the device at these or any other conditions above those indicated in the operation section of this specifi ...

Page 3

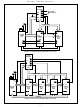

... MA3 MA4 MA5 CLOCK 1 MRD 8 MWR FIGURE 1. FUNCTIONAL DIAGRAM FOR THE CDP1881C CDP1881C, CDP1882, CDP1882C - + 5%, Except as Noted: (Continued CONDITIONS CDP1882 V V (NOTE (V) (V) MIN TYP ...

Page 4

... NOTE: 1. CDP1881C Only Logic 1 = High, Logic 0 = Low Don’t Care Dynamic Electrical Specifications PARAMETER Minimum Setup Time Memory Address to CLOCK Minimum Hold Time Memory Address After CLOCK Minimum CLOCK Pulse Width CDP1881C, CDP1882, CDP1882C ...

Page 5

... For CDP1881C type only. CE CS0, CS1, CS2, CS3 (A) CHIP ENABLE TO CHIP SELECT PROPAGATION DELAY MRD OR MWR CS0, CS1, CS2, CS3 (B) MRD OR MWR TO CHIP SELECT PROPAGATION DELAY (CDP1881C ONLY) MA0 - MA5 CLOCK t CS0, CS1, CS2, CS3 A8 - A11 (C) MEMORY ADDRESS SETUP AND HOLD TIME ...

Page 6

... CE: CHIP ENABLE input - a low at the CE input of CDP1882, CDP1882C will enable the chip select decoder. A low at the CE input of CDP1881C, coincident with a low at either MRD or MRW pin, will enable the chip select decoder. A high on this pin forces CS0, CS1, CS2, and CS3 to a high (false) state ...

Page 7

... CDP1881C, CDP1882, CDP1882C WAIT CLR TPA CDP1800 ADDRESS BUS SERIES CPU MRD MWR FIGURE 5. CDP1800-SERIES SYSTEM USING THE CDP1882 CDP1882 LATCH/ DECODER CS3 CLK CS2 CS1 CE CS0 MA0 - MA5 A8 - A11 WAIT CLR A8 - A11 TPA CS2 ADDRESS BUS CDP1800 CDM5332 SERIES ...

Page 8

... For information regarding Intersil Corporation and its products, see web site http://www.intersil.com Sales Office Headquarters NORTH AMERICA Intersil Corporation P. O. Box 883, Mail Stop 53-204 Melbourne, FL 32902 TEL: (407) 724-7000 FAX: (407) 724-7240 CDP1881C, CDP1882, CDP1882C EUROPE Intersil SA Mercure Center 100, Rue de la Fusee 1130 Brussels, Belgium TEL: (32) 2.724.2111 FAX: (32) 2.724.22.05 ...