ML6652CH Micro Linear, ML6652CH Datasheet

ML6652CH

Available stocks

Related parts for ML6652CH

ML6652CH Summary of contents

Page 1

GENERAL DESCRIPTION The ML6652 is a low cost/low LED current drive single chip Media Converter that provides 10Mbps and 100Mbps signal conversion between twisted pair and fiber optic Ethernet technologies. The device supports conversion between: 10Base-T and 10Base-FL 100Base-TX and ...

Page 2

... Order Information .......................................................................................................................................................... 28 WARRANTY Micro Linear makes no representations or warranties with respect to the accuracy, utility, or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice. No license, express or implied, by estoppel or otherwise, to any patents or other intellectual property rights is granted by this document ...

Page 3

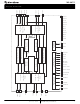

BLOCK DIAGRAM January 2002 Preliminary Datasheet ML6652 GNDB GNDQ VCCQ GNDFC VCCFC VCCL GNDL VCCD GNDD GNDE VCCE GNDT MDIO MDC DUPLEX SPEED AD10 AD32 AD4LIW PECLQU PECLTP TPOUTOFF# FOOUTOFF# PWRDWN# BCKLINK TPINSPD TPANDT FOINSPD FOANDT 3 ...

Page 4

PIN CONFIGURATION PIN DESCRIPTIONS Signal names followed by "#" indicate active low input. Pin No. Signal Name I/O CONFIGURATION 4 AD4LIW I 5 AD32 I 4 Preliminary Datasheet ML6652 44-Pin TQFP (H44-10 ...

Page 5

PIN DESCRIPTIONS (continued) Pin No. Signal Name I/O 6 AD10 ...

Page 6

PIN DESCRIPTIONS (continued) Pin No. Signal Name I/O 8 PECLQU ...

Page 7

PIN DESCRIPTIONS (continued) Pin No. Signal Name I/O 27 SPEED ...

Page 8

PIN DESCRIPTIONS (continued) Pin No. Signal Name I/O CONTROL 13 TPOUTOFF# I (CMOS) 14 FOOUTOFF# I (CMOS) 24 PWRDWN# I (CMOS) DATA SIGNAL INPUT/OUTPUT 1 TPOUTP O 3 TPOUTN O 38 RTTP I 10 TPINP I 11 TPINN I 8 ...

Page 9

PIN DESCRIPTIONS (continued) Pin No. Signal Name I/O Figure 1. Twisted Pair Interface Mode Input Networks 37 REQSD I 39 SDTH I 21 IOUT O 22 IOUT# O Description 1500pF 10 200 From Input Transformer Circuit 200 Pulse H1019 or ...

Page 10

PIN DESCRIPTIONS (continued) Pin No. Signal Name I/O 36 RTOP O 33 FOINP I 32 FOINN I 30 CQOS 10 Preliminary Datasheet Description IOUT# (pin 22) is optionally used to provide current peaking. If peaking is implemented off-chip ...

Page 11

PIN DESCRIPTIONS (continued) Pin No. Signal Name I/O 29 SDFO I BACKUP LINK FUNCTION 40 BCKPLINK I/O LED STATUS 41 TPINSPD O 42 FOINSPD O 43 TPANDT O Description The two operating modes available for this pin are selected with ...

Page 12

PIN DESCRIPTIONS (continued) Pin No. Signal Name I/O LED STATUS (CONTINUED) 44 FOANDT O MANAGEMENT INTERFACE 16 MDIO 17 MDC REFERENCE CLOCK 18 REFCLK POWER AND GROUND 2 GNDT 12 GNDE 15 GNDD 20 GNDL 28 GNDFC 34 GNDQ 35 ...

Page 13

GENERAL DESCRIPTION The ML6652 Fast Ethernet Media Converter provides signal conversion between the following standards: • 10BASE-T to 10BASE-FL; (10Mbps twisted pair copper media and 10Mbps 850nm fiber media) • Proprietary 10BASE-T to 10BASE-1300nm Fiber; (10Mbps twisted pair copper media ...

Page 14

FUNCTIONAL DESCRIPTION DEVICE CONFIGURATION Configuring the ML6652 Media Converter is accomplished through input configuration pins or bits in management control register 30. Configuration pins AD4LIW, AD32 and AD10 determine the PHY address used with the serial management interface consisting of ...

Page 15

FUNCTIONAL DESCRIPTION SPEED SELECTION The Operating modes, FORCED, TRANSPARENT and NON-TRANSPARENT are chosen at power up by setting of the DUPLEX and SPEED pins. Thereafter the operating modes may be set by toggling bits in management register 30. DUPLEX and ...

Page 16

OPERATING MODES Operating Modes are: 1) Forced 10 0 (zero) Volt input on SPEED (or the equivalent Reg. 30 settings) enables only FORCED 10Mbps operation. 100Mbps and Auto-Negotiation are disabled. Link Integrity Warning (LIW) can also be enabled. 2) Forced ...

Page 17

OPERATING MODES TRANSPARENT or NON-TRANSPARENT Mode of operation. Transparent Mode is the default mode of operation for the ML6652 when DUPLEX input is VCC this mode, the control circuit implements the state diagrams of the Auto-Negotiation sub-layer defined ...

Page 18

OPERATING MODES (without thoroughly understanding your PCB layout power up dynamics the safest course is to make short connections and do not to add decoupling capacitors to these pins). When Pin 7 (PECLTP) and Pin 8 (PECLQU) are connected to ...

Page 19

OPERATING MODES resistor is connected to ground and a 1nf capacitor is connected to IOUT to determine the peaking current waveform. If peaking is not implemented, IOUT# should be connected directly to VCC. The preferred mode of operation is PECL/LVPECL ...

Page 20

OPERATING MODES ...

Page 21

CONTROL REGISTERS Control Registers Register 31 ADDR 11111 (bin) 1F (hex) All bits are R/W All bits default to 0 Bit Name Description 15 Power Down Setting bit to 1 powers down all circuits and resets all control logic. Register ...

Page 22

CONTROL REGISTERS Control Registers Register 30 Continued Bit Name Description 9 SINGLESPEED Setting this bit to 1 enables only a single data rate 8 SEL 10Mbps Setting bit to 1 and SINGLESPEED <30.9> enables only 10Mbps data rate ...

Page 23

STATUS REGISTERS Status Registers Register 27 ADDR 11011 (bin) 1B (hex) All bits are Read Only Bit Name Description 15 FOFORCELO This bit set high when the fiber optic input PLL follows the local oscillator 14 FOBADFREQ This bit set ...

Page 24

ELECTRICAL CHARACTERISTICS ABSOLUTE MAXIMUM RATINGS Absolute maximum ratings are those values beyond which the device could be permanently damaged. Absolute maximum ratings are stress ratings only and functional device operation is not implied. Junction Temperature .............................................. 150ºC Storage Temperature Range ...

Page 25

ELECTRICAL TABLES (CONTINUED) SYMBOL PARAMETER 3-LEVEL CONFIGURATION INPUTS: SPEED AND DUPLEX High Input Level Middle Input Level Low Input Level 4-LEVEL CONFIGURATION INPUTS: PECLTP, PECLQU, AF4LIW, AD32, AD10 High Input Level Middle High Input Level Middle Low Input Level Low ...

Page 26

ELECTRICAL TABLES (CONTINUED) SYMBOL PARAMETER [I(TPoutP)+I(TPoutN)]/2 Off State Output Current RTTP Input Current FIBER OPTIC RECEIVER: FOINP, FOINN, CQOS Common-Mode Voltage Differential Input Resistance FIBER OPTIC TRANSMITTER: IOUT, IOUT#, RTOP High Light State Output Current Low Light State Output Current ...

Page 27

ELECTRICAL TABLES (CONTINUED) SYMBOL PARAMETER Signal Detect Assertion Threshold (continued) Voltage Threshold Hysteresis Input Referred Offset Input Referred Noise FIBER OPTIC RECEIVER: FOINP AND FOINN Input Amplifier –3 dB Bandwidth CONDITIONS High bandwidth, 100Mbps, Short Wave Length High bandwidth, 100Mbps, ...

Page 28

... BSC (0.80 BSC) inches (millimeters) ORDERING INFORMATION PART NUMBER TEMPERATURE RANGE ML6652CH 0ºC to 70ºC ML6652EH -20ºC to 85ºC Headquarters: 2050 Concourse Drive, San Jose, CA 95131 (408) 433-5200 www.microlinear.com WESTERN UNITED STATES Micro Linear Corporation 2050 Concourse Drive San Jose, CA 95131 ...