IDTIDT71P71604167BQ IDT [Integrated Device Technology], IDTIDT71P71604167BQ Datasheet

IDTIDT71P71604167BQ

Related parts for IDTIDT71P71604167BQ

IDTIDT71P71604167BQ Summary of contents

Page 1

Features 18Mb Density (1Mx18, 512kx36) Common Read and Write Data Port Dual Echo Clock Output 2-Word Burst on all SRAM accesses Multiplexed Address Bus - One Read or One Write request per clock cycle DDR (Double Data Rate) Data Bus ...

Page 2

IDT71P71804 (1M x 18-Bit) 71P71604 (512K x 36-Bit DDR II SRAM Burst of 2 The K and K clocks are the primary device input clocks. The K clock is used to clock in the control signals (LD, R/W ...

Page 3

IDT71P71804 (1M x 18-Bit) 71P71604 (512K x 36-Bit DDR II SRAM Burst of 2 Pin Definitions Symbol Pin Function Data I/O signals. Data inputs are sampled on the rising edge of K and K during valid write operations. ...

Page 4

IDT71P71804 (1M x 18-Bit) 71P71604 (512K x 36-Bit DDR II SRAM Burst of 2 Pin Definitions continued Symbol Pin Function DLL Turn Off. When low this input will turn off the DLL inside the device. The AC timings ...

Page 5

IDT71P71804 (1M x 18-Bit) 71P71604 (512K x 36-Bit DDR II SRAM Burst of 2 Pin Configuration IDT71P71804 ( ...

Page 6

IDT71P71804 (1M x 18-Bit) 71P71604 (512K x 36-Bit DDR II SRAM Burst of 2 Pin Configuration IDT71P71604 (512K ...

Page 7

IDT71P71804 (1M x 18-Bit) 71P71604 (512K x 36-Bit DDR II SRAM Burst of 2 Write Descriptions (1,2,3) Signal 0 BW Write Byte 0 L Write Byte 1 X Write Byte 2 X Write Byte 3 X NOTES: 1) ...

Page 8

IDT71P71804 (1M x 18-Bit) 71P71604 (512K x 36-Bit DDR II SRAM Burst of 2 Application Example R Data Bus Address LD R MEMORY CONTROLLER Return CLK V t Source CLK ...

Page 9

IDT71P71804 (1M x 18-Bit) 71P71604 (512K x 36-Bit DDR II SRAM Burst of 2 Absolute Maximum Ratings Symbol Rating Supply Voltage on V with DD V TERM Respect to GND Supply Voltage on V with DDQ V TERM ...

Page 10

IDT71P71804 (1M x 18-Bit) 71P71604 (512K x 36-Bit DDR II SRAM Burst Electrical Characteristics Over the Operating Temperature and Supply Voltage Range Parameter Symbol Input Leakage Current I IL Output Leakage Current I OL Operating ...

Page 11

IDT71P71804 (1M x 18-Bit) 71P71604 (512K x 36-Bit DDR II SRAM Burst of 2 Input Electrical Characteristics Over the Operating Temperature and Supply Voltage Range PARAMETER SYMBOL Input High Voltage (DC Input Low Voltage, ...

Page 12

IDT71P71804 (1M x 18-Bit) 71P71604 (512K x 36-Bit DDR II SRAM Burst Test Conditions (1) Parameter Symbol Core Power Supply Voltage V DD I/O Power Supply Voltage V DDQ Input High Level V IH Input ...

Page 13

IDT71P71804 (1M x 18-Bit) 71P71604 (512K x 36-Bit DDR II SRAM Burst Electrical Characteristics Symbol Parameter Clock Parameters t Clock Cycle Time (K,K,C,C) KHKH t Clock Phase Jitter (K,K,C,C) KC var t Clock High Time ...

Page 14

IDT71P71804 (1M x 18-Bit) 71P71604 (512K x 36-Bit DDR II SRAM Burst of 2 Timing Waveform of Combined Read and Write Cycles NOP Read A0 Read A1 (burst of 2) (burst tKHKL ...

Page 15

IDT71P71804 (1M x 18-Bit) 71P71604 (512K x 36-Bit DDR II SRAM Burst of 2 IEEE 1149.1 TEST ACCESS PORT AND BOUNDARY SCAN-JTAG This part contains an IEEE standard 1149.1 Compatible Test Access Port (TAP). The package pads are ...

Page 16

IDT71P71804 (1M x 18-Bit) 71P71604 (512K x 36-Bit DDR II SRAM Burst of 2 Scan Register Definition Part Instrustion Register 512K x36 3 bits 1Mx18 3 bits Identification Register Definitions INSTRUCTION FIELD ALL DEVICES Revision Number (31:29) Device ...

Page 17

IDT71P71804 (1M x 18-Bit) 71P71604 (512K x 36-Bit DDR II SRAM Burst of 2 Boundary Scan Exit Order (1M x 18-Bit) ORDER PIN ...

Page 18

IDT71P71804 (1M x 18-Bit) 71P71604 (512K x 36-Bit DDR II SRAM Burst of 2 Boundary Scan Exit Order (512K x 36-Bit) ORDER PIN ...

Page 19

IDT71P71804 (1M x 18-Bit) 71P71604 (512K x 36-Bit DDR II SRAM Burst of 2 JTAG DC Operating Conditions Parameter Symbol I/O Power Supply V DDQ Power Supply Voltage V DD Input High Level V IH Input Low Level ...

Page 20

IDT71P71804 (1M x 18-Bit) 71P71604 (512K x 36-Bit DDR II SRAM Burst of 2 JTAG AC Characteristics Parameter Symbol TCK Cycle Time t CHCH TCK High Pulse Width t CHCL TCK Low Pulse Width t CLCH TMS Input ...

Page 21

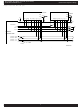

IDT71P71804 (1M x 18-Bit) 71P71604 (512K x 36-Bit DDR II SRAM Burst of 2 Package Diagram Outline for 165-Ball Fine Pitch Grid Array Commercial Temperature Range 6.42 21 ...

Page 22

IDT71P71804 (1M x 18-Bit) 71P71604 (512K x 36-Bit DDR II SRAM Burst of 2 Ordering Information IDT 71P71XXX S XXX Device Power Speed Type CORPORATE HEADQUARTERS 6024 Silver Creek Valley Road San Jose, CA 95138 “QDR SRAMs and ...

Page 23

IDT71P71804 ( -Bit) 71P71604 (512K x 36-Bit DDR II SRAM Burst of 2 Revision History REVISION DATE 0 07/29/05 A 04/21/06 PAGES DESCRIPTION 1-24 Released Final datasheet 1-3,7,8,10,13, Removed 2Mx8 (71P71204) and 2Mx9 (71P71104) device ...