598DAC000716DG Silicon Labs, 598DAC000716DG Datasheet

598DAC000716DG

Specifications of 598DAC000716DG

Related parts for 598DAC000716DG

598DAC000716DG Summary of contents

Page 1

Features programmable output frequencies from 10 to 810 MHz 0.5 ps RMS phase jitter Superior power supply rejection: 0.3–0.4 ps additive jitter Available LVPECL, CMOS, LVDS, ...

Page 2

Si598/Si599 2 Rev. 1.0 ...

Page 3

T C ABLE O F ONTENTS Section 1. Detailed Block Diagrams . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ...

Page 4

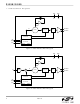

Si598/Si599 1. Detailed Block Diagrams RFREQ OE Control SDA Interface SCL NVM RAM Figure 1. Si598 Detailed Block Diagram + ADC V C VCADC RFREQ OE Control SDA Interface SCL NVM RAM Figure 2. Si599 Detailed Block Diagram 4 f ...

Page 5

Electrical Specifications Table 1. Recommended Operating Conditions Parameter 1 Supply Voltage Supply Current 2 Output Enable (OE) , Serial Data (SDA), Serial Clock (SCL) Operating Temperature Range Notes: 1. Selectable parameter specified by part number. See Section 7. Ordering ...

Page 6

Si598/Si599 Table 3. CLK± Output Frequency Characteristics (Typical values º 3.3 V, min/max limits VDD = 1.8 ±5%, 2.5 or 3.3 V ±10 – ºC unless otherwise DD noted) Parameter Symbol ...

Page 7

Table 4. CLK± Output Levels and Symmetry (Typical values º 3.3 V, min/max limits VDD = 1.8 ±5%, 2.5 or 3.3 V ±10 – ºC unless otherwise DD noted) Parameter Symbol ...

Page 8

Si598/Si599 Table 5. CLK± Output Phase Jitter (Si598) (Typical values º 3.3 V, min/max limits VDD = 1.8 ±5%, 2.5 or 3.3 V ±10 – ºC unless otherwise DD noted) Parameter ...

Page 9

Table 7. CLK± Output Period Jitter (Typical values º 3.3 V unless otherwise noted) DD Parameter Symbol J Period Jitter* PER *Note: Any output mode, including CMOS, LVPECL, LVDS, CML 1000 cycles. Table ...

Page 10

Si598/Si599 Table 11. Environmental Compliance The Si598/599 meets the following qualification test requirements. Parameter Mechanical Shock Mechanical Vibration Solderability Gross & Fine Leak Resistance to Solder Heat Moisture Sensitivity Level Contact Pads Table 12. Programming Constraints and Timing (Typical values ...

Page 11

Table 13. Thermal Characteristics (Typical values º 3 Parameter Thermal Resistance Junction to Ambient Thermal Resistance Junction to Case Ambient Temperature Junction Temperature Table 14. Absolute Maximum Ratings Parameter Supply Voltage, 1.8 V ...

Page 12

Si598/Si599 3. Functional Description The Si598 XO and the Si599 VCXO are low-jitter oscillators ideally suited for applications requiring programmable frequencies. The programmed to generate any output clock in the range 810 MHz with frequency resolution of ...

Page 13

A typical frequency configuration for this example: RFREQ = 0x8858199E9 current F = 148.35 MHz out_current F = 148.50 MHz out_new Calculate RFREQ to change the output frequency new from 148.35 to 148.5 MHz: RFREQ 0x8858199E9 = new 0x887B6473C ...

Page 14

Si598/Si599 3. Unfreeze the DCO and assert the NewFreq bit (bit 6 of Register 135) within the maximum Unfreeze to NewFreq Timeout in Table 12, “Programming Constraints and Timing,” on page 10. The process of freezing and unfreezing the DCO ...

Page 15

Serial Port Registers Note: Registers not documented are reserved. Values within reserved registers and reserved bits must not be changed. Register Name Bit 7 7 High Speed/ N1 Dividers 8 Reference N1[1:0] Frequency 9 Reference Frequency 10 Reference Frequency ...

Page 16

Si598/Si599 Register 7. High Speed/N1 Dividers Bit D7 D6 HS_DIV[2:0] Name R/W Type Bit Name 7:5 HS_DIV[2:0] DCO High Speed Divider. Sets value for high speed divider that takes the DCO output f 000 = 4 001 = 5 010 ...

Page 17

Register 9. Reference Frequency Bit D7 D6 Name Type Bit Name 7:0 RFREQ[31:24] Reference Frequency. Frequency control input to DCO. Register 10. Reference Frequency Bit D7 D6 Name Type Bit Name 7:0 RFREQ[23:16] Reference Frequency. Frequency control input to DCO. ...

Page 18

Si598/Si599 Register 12. Reference Frequency Bit D7 D6 Name Type Bit Name 7:0 RFREQ[7:0] Reference Frequency. Frequency control input to DCO. Register 135. NewFreq/Freeze/Memory Control Bit D7 D6 NewFreq Name R/W R/W Type Reset settings = 00xxxx00 Bit Name 7 ...

Page 19

Register 137. Freeze DCO Bit D7 D6 Name R/W R/W Type Reset settings = Si598: 0000xxxx, Si599: 1000xxxx Bit Name 7 Reserved 0: Si598 1: Si599 6:5 Reserved This bits should read 0 in normal operation. 4 Freeze DCO Freeze ...

Page 20

Si598/Si599 5. Si598 (XO) Pin Descriptions Pin Name GND 4 CLK+ CLK– 5 (NC for CMOS SDA 8 SCL *Note: OE pin includes a 17 k resistor (Top ...

Page 21

Si599 (VCXO) Pin Descriptions Pin Name GND 4 CLK+ CLK– 5 (NC for CMOS SDA 8 SCL *Note: OE pin includes a 17 k resistor to V (Top View) ...

Page 22

Si598/Si599 7. Ordering Information The Si598/Si599 supports a wide variety of options including frequency range, start-up frequency, temperature stability, tuning slope, output format, and V at time of shipment. Configurations are specified using the Part Number Configuration chart shown below. ...

Page 23

Table 17. Standard Si598 Part Numbers Part Number VDD 598CCC000107DG 3.3V 598BCA000107DG 3.3V Output Total Stability Frequency Format Range CMOS 30 ppm 10–160 MHz LVDS 30 ppm 10–810 MHz Rev. 1.0 Si598/Si599 Startup Address Frequency 10 MHz ...

Page 24

Si598/Si599 8. Si59x Mark Specification Figure 6 illustrates the mark specification for the Si59x. Table 18 lists the line information. Table 18. Si59x Top Mark Description Line Position 1 1–10 “SiLabs"+ Part Family Number, 59x (first 3 characters in ...

Page 25

Outline Diagram and Suggested Pad Layout Figure 7 illustrates the package details for the Si598/Si599. Table 19 lists the values for the dimensions shown in the illustration. Figure 7. Si598/Si599 Outline Diagram Table 19. Package Diagram Dimensions (mm) ...

Page 26

Si598/Si599 10. 8-Pin PCB Land Pattern Figure 8 illustrates the 8-pin PCB land pattern for the Si598/Si599. Table 20 lists the values for the dimensions shown in the illustration. Figure 8. Si598/Si599 PCB Land Pattern Table 20. PCB Land Pattern ...

Page 27

OCUMENT HANGE IST Revision 0.2 to Revision 0.9 Updated Si598/599 devices to support frequencies 810 MHz for LVPECL, LVDS, and CML outputs. Added Table 13, “Thermal Characteristics,” on page 11. Updated ESD HBM ...

Page 28

... Should Buyer purchase or use Silicon Laboratories products for any such unintended or unauthorized ap- plication, Buyer shall indemnify and hold Silicon Laboratories harmless against all claims and damages. Silicon Laboratories, Silicon Labs, and DSPLL are trademarks of Silicon Laboratories Inc. Other products or brandnames mentioned herein are trademarks or registered trademarks of their respective holders. ...