CY7C1021DV33-10BVXI Cypress Semiconductor Corp, CY7C1021DV33-10BVXI Datasheet

CY7C1021DV33-10BVXI

Specifications of CY7C1021DV33-10BVXI

Available stocks

Related parts for CY7C1021DV33-10BVXI

CY7C1021DV33-10BVXI Summary of contents

Page 1

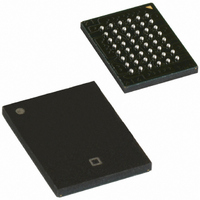

... HIGH), the outputs are disabled (OE HIGH), the BHE and BLE are disabled (BHE, BLE HIGH), or during a Write operation (CE LOW, and WE LOW). The CY7C1021DV33 is available in Pb-free 44-pin 400-Mil wide Molded SOJ, 44-pin TSOP II and 48-ball VFBGA packages. DATA IN DRIVERS ...

Page 2

... NC pins are not connected on the die. Document #: 38-05460 Rev. *F –10 (Industrial/Automotive- 48-ball VFBGA Top View BLE OE BHE I/O BLE BHE 8 I/O 15 I/O I I I/O 10 I/O 9 I/O I CY7C1021DV33 [2] –12 (Automotive-E) Unit 12 ns 100 I I ...

Page 3

... CE > V – 0.3V > V – 0. < 0.3V Test Conditions T = 25 MHz 3. Test Conditions Still Air, soldered × 4.5 inch, four-layer printed circuit board CY7C1021DV33 Ambient V Speed CC Temperature 3.3V 0.3V – + – + –12 (Auto-E) Unit Max. Min. Max. 2.4 V 0.4 ...

Page 4

... AC characteristics (except High-Z) are tested using the load conditions shown in Figure (a). High-Z characteristics are tested for all speeds using the test load shown in Figure (c). Document #: 38-05460 Rev. *F [6] 3.0V 30 pF* GND Rise Time: 1 V/ns High-Z characteristics: R 317 3.3V OUTPUT 351 (c) CY7C1021DV33 ALL INPUT PULSES 90% 90% 10% 10% Fall Time: 1 V/ns (b) Page [+] Feedback ...

Page 5

... Write. The input data set-up and hold timing should be referenced to the leading edge of the signal that terminates the Write. Document #: 38-05460 Rev. *F [7] -10 (Ind’l/Auto-A) Min. Max. 100 values until the first memory access can be performed less than less than t , and t HZCE LZCE HZOE LZOE HZWE CY7C1021DV33 -12 (Auto-E) Min. Max. Unit s 100 ...

Page 6

... > V – 0. < 0. DATA RETENTION MODE 3.0V > CDR [14, 15 OHA t RC DOE DATA VALID 50% > 50 s or stable at V > 50 CC(min.) CC(min CY7C1021DV33 Min. Max. Unit 2 V Industrial 3 mA Automotive 3. DATA VALID t HZOE t HZCE t HZBE HIGH IMPEDANCE 50 Page [+] Feedback ...

Page 7

... Write Cycle No. 2 (BLE or BHE Controlled) ADDRESS t SA BHE, BLE WE CE DATA I/O Notes 17. Data I/O is high impedance BHE and/or BLE = V 18 goes HIGH simultaneously with WE going HIGH, the output remains in a high-impedance state. Document #: 38-05460 Rev SCE PWE PWE t SCE CY7C1021DV33 Page [+] Feedback ...

Page 8

... Read – Lower bits only Data Out Read – Upper bits only Data In Write – All bits High-Z Write – Lower bits only Data In Write – Upper bits only High-Z Selected, Outputs Disabled High-Z Selected, Outputs Disabled CY7C1021DV33 LZWE Mode Power Standby ( Active (I ...

Page 9

... Ordering Information Speed (ns) Ordering Code 10 CY7C1021DV33-10VXI CY7C1021DV33-10ZSXI CY7C1021DV33-10BVXI 10 CY7C1021DV33-10ZSXA 12 CY7C1021DV33-12ZSXE Ordering Code Definitions V33 - XX XXX Please contact your local Cypress sales representative for availability of these parts. Document #: 38-05460 Rev. *F Package Package Type Name 51-85082 44-pin (400-Mil) Molded SOJ (Pb-free) 51-85087 44-pin TSOP Type II (Pb-free) ...

Page 10

... Package Diagrams Figure 1. 44-pin (400-Mil) Molded SOJ (51-85082) Figure 2. 44-pin Thin Small Outline Package Type II (51-85087) Document #: 38-05460 Rev. *F CY7C1021DV33 51-85082 *C 51-85087 *C Page [+] Feedback ...

Page 11

... Package Diagrams (continued) Figure 3. 48-ball VFBGA ( mm) (51-85150) All products and company names mentioned in this document are the trademarks of their respective holders. Document #: 38-05460 Rev. *F CY7C1021DV33 51-85150 *F Page [+] Feedback ...

Page 12

... Document History Page Document Title: CY7C1021DV33, 1-Mbit (64K x 16) Static RAM Document Number: 38-05460 REV. ECN NO. Issue Date ** 201560 See ECN *A 233693 See ECN *B 263769 See ECN *C 307601 See ECN *D 520652 See ECN *E 2898399 03/24/2010 *F 3109897 12/14/2010 Document #: 38-05460 Rev. *F Orig. of ...

Page 13

... The inclusion of Cypress products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges. cypress.com/go/plc CY7C1021DV33 PSoC Solutions psoc.cypress.com/solutions ...