ISPPAC-POWR1208-01T44I Lattice, ISPPAC-POWR1208-01T44I Datasheet

ISPPAC-POWR1208-01T44I

Specifications of ISPPAC-POWR1208-01T44I

Available stocks

Related parts for ISPPAC-POWR1208-01T44I

ISPPAC-POWR1208-01T44I Summary of contents

Page 1

... The Lattice ispPAC-POWR1208 incorporates both in- system programmable logic and in-system programma- ble analog circuits to perform special functions for power supply sequencing and monitoring. The ispPAC- POWR1208 device has the capability to be configured through software to control up to eight outputs for power ...

Page 2

... The ispPAC-POWR1208 device contains an internal PLD that is programmable by the user to implement digital logic functions and control state machines. The internal PLD connects to four programmable timers, special purpose I/O and the programmable monitoring circuit blocks ...

Page 3

... Analog Input 34 VMON3 Analog Input 35 VMON4 Analog Input 36 VMON5 Analog Input 37 VMON6 Analog Input 38 VMON7 Analog Input ispPAC-POWR1208 Data Sheet Voltage Range 2 2.25V-5.5V Open-drain Output 4 3 8V-12V FET Gate Driver 4 2 2.25V-5.5V Open-drain Output 3 3 8V-12V FET Gate Driver 3 2 2.25V-5.5V ...

Page 4

... RESET connected to the POR pin can be used if multiple ispPAC-POWR1208 devices are cascaded together in expansion mode manual reset button is needed to reset the PLD logic to the initial state. While using the ispPAC-POWR1208 in hot-swap applications it is recommended that either the RESET pin be connected to the POR pin, or connect a capacitor to ground (such that the time constant with the pull-up resistor) from the RESET pin. 8. The CREF pin requires a 0.1µ ...

Page 5

... APROG programming T Ambient temperature A 1. The ispPAC-POWR1208 device must be powered from 3.0V to 5.5V during programming of the the supply pin that controls logic inputs IN1-IN4 only. Place 0.1µF capacitor to ground and supply the V DDINP supply voltage for the given input logic range. ...

Page 6

... FET Driver mode SOURCE +85°C to +125°C (Note 3) -40°C to +125°C SOURCE I > 0.5µA SOURCE FET Driver in OFF state V = 2.25V DD DD. Conditions V ramping ramping up DD DD. 6 ispPAC-POWR1208 Data Sheet Min. Typ. Max. 8 — 12 -10 — 10 — 0.5 — 0.5 — 50 5.45 — 50 — 10 — ...

Page 7

... Over Recommended Operating Conditions Conditions 0V ≤ V ≤ DDINP 25 °C 25 ° 4mA SINKOUT (Note 1) (Note 1) (Note 1) V (V) IL Min. Max. -0.3 0.8 -0.3 0.7 7 ispPAC-POWR1208 Data Sheet Min. Typ. — 100mV TRIP — 100mV TRIP 230 — 1.95 — — — 0.03 — Min. Typ. Max ...

Page 8

... Note: All the above parameters apply to signal paths from the digital inputs [IN1-IN4]. Over Recommended Operating Conditions Conditions Applied to IN1-IN4 Stable input before clock edge (Note 1) Data valid before clock (Note 1) Hold data after clock . DD 8 ispPAC-POWR1208 Data Sheet Min. Typ. Max. 20 300 Units µs ns µ ...

Page 9

... DIS DIH DOZH DOV t DO Conditions 1 2 CMOS cells. t CKMIN MSS DOXZ 9 ispPAC-POWR1208 Data Sheet Min Typ. Max 1 200 200 200 200 200 40 40 100 40 100 t t PWP, PWE t MSS Program and Erase cycles executed in Run-Test/Idle Units µ ...

Page 10

... Comparator Trip Point MON Accuracy vs. Temperature - Temperature (°C) 10 ispPAC-POWR1208 Data Sheet Propagation Delay vs. Overdrive Glitch Filter = 20µs Glitch Filter = 5µ Input Overdrive (mV) Note: Typical propagation delay of V inputs to outputs MON as a function of overdrive beyond selected trip point. ...

Page 11

... Each of the twelve comparators are independently set in the same way. Theory Of Operation The ispPAC-POWR1208 incorporates programmable voltage monitors along with digital inputs and outputs as well as high voltage FET gate drivers to control MOSFETs for ramping up power supply rails. The 16 macrocell PLD inputs are from the 12 voltage monitors and four digital inputs. There are four embedded programmable timers that interface with the PLD, along with an internal programmable oscillator ...

Page 12

... PLD Architecture The ispPAC-POWR1208 digital logic is composed of an internal PLD that is programmed to perform the sequenc- ing functions. The PLD architecture allows flexibility in designing various state machines and control logic used for monitoring ...

Page 13

... The macrocell also supports asynchronous reset and preset functions, derived from either product terms, the global reset input or the power-on reset signal. Figure 3. ispPAC-POWR1208 Macrocell Block Diagram Block Init Product Term PT4 ...

Page 14

... VMON[1:12] Comparators 4 IN[1: AND Array 36 Inputs 81 PTs 16 Outputs BLK-INIT PT Timer1 Timer2 Routing Pool Timer3 Timer4 Clock Generation 14 ispPAC-POWR1208 Data Sheet MC0 HVOUT1 MC1 HVOUT2 HVOUT3 MC2 HVOUT4 MC3 MC4 OUT5 MC5 OUT6 Output OUT7 MC6 Routing OUT8 MC7 Pool MC8 MC9 ...

Page 15

... Lattice Semiconductor Clock and Timer Systems Figure 5 shows a block diagram of the ispPAC-POWR1208’s internal clock and timer systems. The PLD clock can be programmed with eight different frequencies based on the internal oscillator frequency of 250kHz. Figure 5. Clock and Timer Block Internal OSC 250kHz ...

Page 16

... Timer Period Timer Reset Expired Timer ProgrammableTimer Delay 16 ispPAC-POWR1208 Data Sheet ÷ ÷ ÷ ÷ 128 ÷ ÷ ÷ ÷ 256 2 kHz 1 kHz 1.024 ms 2.048ms 2.048ms 4.096 ms 4.096 ms 4.096 ms 8.192 ms 8.192 ms 8.192 ms 16.384 ms 16.384 ms 16 ...

Page 17

... Output Configuration Modes The output pins for the ispPAC-POWR1208 device are programmable for different functional modes. The four out- puts HVOUT1-HVOUT4, can be used as FET gate drivers or be programmed as open-drain digital outputs. Figure 7 explains the details of the gate driver mode. ...

Page 18

... S of 6.7V corresponds to ~ gate charge ( when current is constant, gate charging time can be expressed CHARGE-TIME CHARGE-TIME CHARGE-TIME -6 10 ispPAC-POWR1208 Data Sheet 60 ) will therefore be 6.7V. Reading across GS ). Because charge is equal (1) (2) (3) ...

Page 19

... The voltage that the pin is capable of driving to is listed in Table 4. For each supply range, the charge-pump range will be set by the software. Table 4. HVOUT Gate Driver Voltage Range (the software assists this process). This voltage is con 2. 3. 8.5 8 9.5 9 ispPAC-POWR1208 Data Sheet 8.5 9 9 ...

Page 20

... The optional identification (IDCODE) register described in IEEE 1149.1 is also included in the ispPAC-POWR1208. Six additional user data registers are included in the TAP of the ispPAC-POWR1208 as shown in Figure 10. Most of these additional registers are used to program and verify the analog configuration (CFG) and PLD bits. A status register is also provided to read the status of the twelve analog comparators ...

Page 21

... CFG ADDRESS REGISTER (4 bits) PLD DATA REGISTER (81 bits) PLD ADDRESS REGISTER (75 bits) INSTRUCTION REGISTER (6 bits) BYPASS REGISTER (1 bit) TEST ACCESS PORT OUTPUT (TAP) LOGIC LATCH TCK TMS TDO 21 ispPAC-POWR1208 Data Sheet ANALOG CONFIGURATION 2 E NON-VOLATILE MEMORY (164 bits) PLD AND / ARCH E 2 NON-VOLATILE ...

Page 22

... BYPASS and EXTEST instruction code patterns being specifically called out (all ones and all zeroes respec- tively). The ispPAC-POWR1208 contains the required minimum instruction set as well as one from the optional instruction set. In addition, there are several proprietary instructions that allow the device to be configured, verified, and monitored ...

Page 23

... BYPASS is one of the three required instructions. It selects the Bypass Register to be connected between TDI and TDO and allows serial data to be transferred through the device without affecting the operation of the ispPAC- POWR1208. The IEEE 1149.1 standard defines the bit code of this instruction to be all ones (111111). ...

Page 24

... ADDPLD instruction. This instruction also forces the outputs into the SAF- ESTATE. DISCHARGE – This instruction is used to discharge the internal programming supply voltage after an erase or pro- gramming cycle and prepares ispPAC-POWR1208 for a read cycle. This instruction also forces the outputs into the SAFESTATE. Part Number ...

Page 25

... PROGRAMDIS – This instruction disables the programming mode of the ispPAC-POWR1208. The Test-Logic- Reset JTAG state can also be used to cancel the programming mode of the ispPAC-POWR1208. ADDSTATUS – This instruction is used to both connect the status register to TDO (Figure 14) and latch the 12 volt- age monitor (comparator outputs) into the status register. Latching of the 12 comparator outputs into the status reg- ister occurs during Capture-Data-Register JTAG state ...

Page 26

... The comparators can be set with a trip point from 1.03V to 5.72V, with 192 different values. The applica- tion diagram shows a set-up that can monitor and control multiple power supplies. The ispPAC-POWR1208 device controls FET switches to ramp the supplies at different slew rates and time delays. The digital outputs and inputs are also used to interface with the board that is being powered up ...

Page 27

... Lattice Semiconductor Figure 16. Typical Application Example: ispPAC-POWR1208 Driving [4] FET Switches [4] Digital OE/EN Lines -48V DC/DC + Primary Supply - -48V + DC/DC Primary Supply - -48V + DC/DC Primary Supply - -48V + DC/DC Primary Supply - 12 Analog Inputs VMON1 VMON2 VMON3 VMON4 VMON5 VMON6 ispPAC-POWR1208 VMON7 VMON8 Power Sequence VMON9 V DD VMON10 VMON11 ...

Page 28

... PAC-Designer. PAC-Designer is an easy-to-use graphical user interface (Figure 17) that allows the user to set up the ispPAC-POWR1208 to perform given functions, such as timed sequences for power supply and monitor trip points for the voltage monitor inputs. The software tool gives the user control over how the device drives the outputs and the functional confi ...

Page 29

... TAP interface and shifts in the JEDEC data bits that set the configuration of all the analog and digital circuitry that the user has defined during the design process. Power to the device must be set at 3.0V to 5.5V during programming, once the programming steps have been com- pleted, the power supply to the ispPAC-POWR1208 can be set from 2.5V to 5V. Once programmed, the on-chip 2 non-volatile E CMOS bits hold the entire design confi ...

Page 30

... The ispPAC-POWR1208 Design Kit includes an engineering prototype board that can be connected to the parallel port using a Lattice ispDOWNLOAD cable. It demonstrates proper layout techniques for the ispPAC- POWR1208 and can be used in real time to check circuit operation as part of the design process. LEDs are sup- plied to debug designs without involving test equipment. Input and output connections as well as a “ ...

Page 31

... Lattice Semiconductor and interconnect areas with pads for pins or cables. The user can check out designs on the hardware and make necessary changes to the design for the function required. ispPAC-POWR1208 Data Sheet 31 ...

Page 32

... A1 IS DEFINED AS THE DISTANCE FROM THE SEATING PLANE TO THE LOWEST POINT ON THE PACKAGE BODY. EXACT SHAPE OF EACH CORNER IS OPTIONAL. 8. 0. 0.20 H A-B SEE DETAIL 'A' C LEAD FINISH 0. BASE METAL 32 ispPAC-POWR1208 Data Sheet 44X BOTTOM VIEW 0.20 MIN. A1 1.00 REF. DETAIL 'A' SYMBOL MIN. NOM 0. ...

Page 33

... Lattice Semiconductor Part Number Description ispPAC-POWR1208 - 01XX44X Device Family Device Number ispPAC-POWR1208 Ordering Information Conventional Packaging ispPAC-POWR1208-01T44I ispPAC-POWR1208-01T44E Lead-Free Packaging ispPAC-POWR1208-01TN44I ispPAC-POWR1208-01TN44E Industrial Part Number Package TQFP Automotive Part Number Package TQFP Lead-Free Industrial Part Number Package TQFP Lead-Free Automotive Part Number ...

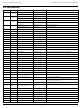

Page 34

... Lattice Semiconductor Package Options HVOUT4 1 HVOUT3 2 HVOUT2 3 HVOUT1 4 VDD 5 ispPAC-POWR1208 IN1 6 44-pin TQFP IN2 7 IN3 8 IN4 9 RESET 10 VDDINP ispPAC-POWR1208 Data Sheet VMON2 33 VMON1 32 TMS 31 TDI 30 TRST 29 TDO 28 GND 27 CLK 26 POR 25 TCK 24 COMP1 23 ...