ADP5020ACPZ-R7 Analog Devices Inc, ADP5020ACPZ-R7 Datasheet

ADP5020ACPZ-R7

Specifications of ADP5020ACPZ-R7

Related parts for ADP5020ACPZ-R7

ADP5020ACPZ-R7 Summary of contents

Page 1

FEATURES Input voltage range: 2 5.5 V Low standby current: 1 μA Switching frequency: 3 MHz interface Synchronous Buck 1 regulator: 600 mA Synchronous Buck 2 regulator: 250 mA Low dropout regulator (LDO): 150 mA ...

Page 2

ADP5020 TABLE OF CONTENTS Features .............................................................................................. 1 Applications ....................................................................................... 1 Typical Applications Circuit ............................................................ 1 General Description ......................................................................... 1 Revision History ............................................................................... 2 Functional Block Diagram .............................................................. 3 Specifications ..................................................................................... 4 Switching Specifications .............................................................. 5 DC-to-DC Conversion Specifications, Buck 1 ...

Page 3

FUNCTIONAL BLOCK DIAGRAM RESET XSHTDN SCL SDA VDD_IO EN/GPIO SYNC THERMAL SHUTDOWN HOUSE- VDDA KEEPING VDD3 VDD2 VDD1 VDDA UVLO CONTROL LOGIC SEQUENCER DGND AGND Figure 2. Rev Page ADP5020 SW1 BUCK ...

Page 4

ADP5020 SPECIFICATIONS T = −40°C to +125° 3 DDx DD_IO Table 1. Parameter OPERATING RANGE VDDx Operating Voltage Range 1 Logic I/O Operating Voltage Range EN, SDA, SCL CHARACTERISTICS Low Level Input Voltage High Level ...

Page 5

SWITCHING SPECIFICATIONS Table 2. Parameter SWITCHING FREQUENCY CH1 CH2 SYNC CLOCK DIVIDER RATIO SYNC CHARACTERISTICS Frequency Range Frequency Duty Cycle Signal DC Coupling Level Low Level Input Voltage High Level Input Voltage DC Coupling AC Coupling Level AC Coupling Capacitor ...

Page 6

ADP5020 DC-TO-DC CONVERSION SPECIFICATIONS, BUCK 2 REGULATOR Table 4. Parameter OUTPUT VOLTAGE 1 Adjustable Range Initial Accuracy Total Accuracy Load Regulation Line Regulation CURRENT Maximum Output Current Quiescent Current POWER Low-Side Power nMOSFET High-Side Power pMOSFET SWITCH CURRENT LIMIT MINIMUM ...

Page 7

I C TIMING SPECIFICATIONS Table 6. Parameter Min Max f 400 SCL t 0.6 HIGH t 1.3 LOW t 100 SU,DAT 0.9 HD,DAT t 0.6 SU,STA t 0.6 HD,STA t 1.3 BUF t 0.6 SU,STO t ...

Page 8

ADP5020 ABSOLUTE MAXIMUM RATINGS Table 7. Parameter VDD1, VDD2, VDD3 SW1, SW2 VOUT1, VOUT2, VOUT3 VDD_IO EN, SCL, SDA, SYNC, XSHTDN Operating Temperature Range Ambient Junction Storage Temperature Range Lead Temperature Soldering (10 sec) Vapor Phase (60 sec) Infrared (15 ...

Page 9

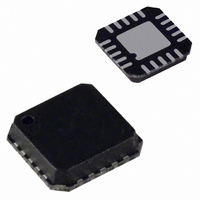

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS VOUT1 15 ADP5020 VOUT1 14 BOTTOM VIEW VDD3 13 (Not to Scale) VOUT3 12 EN/GPIO 11 EXPOSED PAD NOTES 1. EXPOSED PAD SHOULD BE CONNECTED TO PGND1 AND PGND2. Figure 4. Pin Configuration (Bottom View) ...

Page 10

ADP5020 TYPICAL PERFORMANCE CHARACTERISTICS OUT1 OUT2 OUT3 3.5 3.3V 3.0V 3.0 2.8V 2.5V 2.5 2.0V 2.0 1.8V 1.5 1 LOAD CURRENT (mA) Figure 6. ...

Page 11

OUT1 OUT2 OUT3 0.90 0.85 0.80 0.75 0.70 0.65 0.60 0.55 0. 100 150 LOAD CURRENT (mA) Figure 12. Buck 2 Efficiency vs. Load Current BUCK ...

Page 12

ADP5020 OUT1 OUT2 OUT3 LDO OUTPUT = 1V/DIV TIME = 50µs/DIV LDO Figure 18. LDO Startup SW1 BUCK 1 OUTPUT = 20mV/DIV SW1 = 5V/DIV TIME = 100ns/DIV ...

Page 13

THEORY OF OPERATION CIRCUIT OPERATION The buck converters use pMOSFET as the upper switch and nMOSFET as a synchronous rectifier. This synchronous recti- fication maintains high efficiency for a wide input and output voltage range. The voltage mode control architecture, ...

Page 14

ADP5020 CONTROL REGISTERS DEVICE ADDRESS Following a start condition, the bus master must send the address of the slave it is accessing. The slave address for the ADP5020 is shown in Table 10. The Bit 0 defines the operation to ...

Page 15

Table 14. BUCK2_LDO_VSEL Register, Address 0x02 Bit Bit Name Access Default [7:4] BK2_VSEL[3:0] R/W Fuse [3:0] LDO_VSEL[3:0] R/W Fuse Description Sets the voltage output level of the Buck 2 regulator. Preloads on power-up with values stored in fuses. Note that ...

Page 16

ADP5020 Table 15. REG_CONTROL_STATUS Register, Address 0x03 Bit Bit Name Access Default 7 BK1_EN R BK2_EN R LDO_EN R EN_ALL R BK1_PGOOD BK2_PGOOD LDO_PGOOD R 0 ...

Page 17

POWER-UP/POWER-DOWN SEQUENCE SEQUENCER The sequencer is enabled after a low-to-high transition of the enable pin (EN). When EN is low or programmed as an output, the sequencing is controlled and timed by the application processor 2 via the I C ...

Page 18

ADP5020 Activation Waveforms VDDx V UVLOR POR INTERNAL POR SEQUENCER 2 REGISTERS I C BUS PROGRAMMING BUCK 1 LDO BUCK 2 XSHTDN VDDx POR INTERNAL POR SEQUENCER REGISTERS BUS ...

Page 19

POWER-ON SEQUENCE USING THE I When the EN pin is low, the regulator sequence is controlled by 2 the application processor sending I C commands to control the activation. When Bit 4 (EN_ALL) in the REG_CONTROL_ STATUS register (Address 0x03) ...

Page 20

ADP5020 The application processor, together with the regulator power good signal, controls the XSHTDN pin, as shown in Table 18. After a regulator is enabled and no failure condition is detected (power good = 1 in Bits[3:1] of the REG_CONTROL_STATUS ...

Page 21

APPLICATIONS INFORMATION POWER GOOD STATUS The ADP5020 constantly monitors the operating conditions. When a regulator is activated, it checks if the output voltage level is above 80% (the power good threshold) of the nominal level for that output. If the ...

Page 22

ADP5020 LDO INPUT FILTER To improve the LDO input-to-output ripple suppression in the critical switching frequency range of the buck converters, it may be necessary to add an LC filter tuned to 1 MHz, as shown in Figure 28. Additional ...

Page 23

LAYOUT RECOMMENDATIONS APPLICATIONS SCHEMATIC VBATT GND VDDIO R1 R2 10kΩ 10kΩ SDA SCL SYNC GPIO/EN ADP5020 VDD1 C4 10µF SW1 VOUT1 VDD2 VOUT1 PGND1 VDD3 C6 1.0µF VDDA SW2 VOUT2 VDD_IO C5 PGND2 0.1µF VOUT3 SDA SCL SYNC EN/GPIO XSHTDN ...

Page 24

ADP5020 PCB BOARD LAYOUT RECOMMENDATIONS • Place the input and output capacitors, C1, C2, C3, C4, and C5, as close as possible to the respective ADP5020 pin, and make the grounding connection to the ADP5020 ground pins as short as ...

Page 25

... OUTLINE DIMENSIONS PIN 1 INDICATOR 12° MAX 1.00 0.85 0.80 SEATING PLANE ORDERING GUIDE Model Temperature Range 1 ADP5020ACPZ-R7 −40°C to +85°C ADP5020CP-EVALZ RoHS Compliant Part. 0.60 MAX 4.00 BSC SQ 0.60 MAX 15 16 0.50 3.75 BSC BSC SQ (BOTTOM VIEW 0.50 TOP VIEW ...

Page 26

ADP5020 NOTES Rev Page ...

Page 27

NOTES Rev Page ADP5020 ...

Page 28

ADP5020 NOTES ©2009 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D07774-0-5/09(0) Rev Page ...