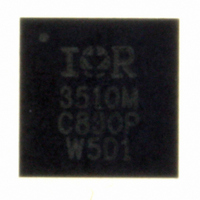

IR3510MTRPBF International Rectifier, IR3510MTRPBF Datasheet

IR3510MTRPBF

Specifications of IR3510MTRPBF

Available stocks

Related parts for IR3510MTRPBF

IR3510MTRPBF Summary of contents

Page 1

DESCRIPTION The IR3510 Hot-Swap N+1 Redundant X-Phase Controller combines input isolation control for hot- swappable application, X-Phase VRM/VRD control and output OR-ing control for N+1 redundant application. It interfaces with microcontroller and X-Phase phase ICs to provide a full featured ...

Page 2

APPLICATION CIRCUIT IRF6635 +12V IN C11 GND 0.1u 1 VCC Cx 0. ENABLE 4 VRRDY 5 ORING 6 VSET 7 OVP_LIMIT 8 OCP_LIMIT IOCD Css 0.1u PACKAGE Page 1m/1W ...

Page 3

ABSOLUTE MAXIMUM RATINGS Operating Junction Temperature…………….. 0 Storage Temperature Range………………….-65 ESD Rating………………………………………HBM Class 1C JEDEC Standard MSL Rating………………………………………3 Reflow Temperature…………………………….260 PIN # PIN NAME 1 VCC ENABLE 4 VRRDY 5 ORING 6 VSET 7 OVPSET 8 OCPSET ...

Page 4

PIN DESCRIPTION PIN# PIN NAME PIN DESCRIPTION 1 VCC Power input for internal circuitry Connect external cap for charge pump 3 ENABLE Enable input. Lower level threshold turns on input FET, Higher level threshold turns on VRM output. ...

Page 5

ELECTRICAL SPECIFICATIONS Unless otherwise specified, these specifications apply over: 8.1V ≤ VCC ≤ 16V, 0 PARAMETER VBIAS Regulator Output Voltage Charge Pump Output Voltage Above VCC Output Voltage Above VCC Voltage Clamp Input UVLO1 Start Threshold Voltage Stop Threshold Voltage ...

Page 6

Input Soft-Start Regulator Gain Transconductance Bandwidth Sink Current Input OC Regulator Input Offset Voltage ICS+ Input Impedance ICS- Bias Current OC Regulator Transconductance OC Regulator Bandwidth OC Time-out Threshold Voltage OC Pull-down Current Severe Over-Current Threshold IOCD Charge Current IOCD ...

Page 7

Voltage Error Amplifier Input Offset Voltage Note 1, VFB Bias Current VSET Bias Current DC Gain Note 2 Bandwidth Note 2 Slew Rate Note 2 Source Current Sink Current Maximum Voltage Minimum Voltage OC Clamping Buffer Input Offset Voltage V(EAOUT)= ...

Page 8

Slew Rate Note 2, Minimum Output Voltage Source Current Sink Current OVP Comparator Threshold Voltage Rising Threshold Voltage Falling Note 2, 0.5V ≤ V(OVPSET) ≤ 4V OVPSET Bias Current OVPSNS Bias Current OVP Delay Time BB Disable Clamp Input Offset ...

Page 9

OR-ing FET Gate Driver GATE_O Pull-up Resistor GATE_O Charge Current Gate Turn-off Time 2V ≤ V(GATE_O) – V(OR+) ≤ 10V Turn-off Delay Time Voltage Clamping General VCC Supply Current Note 1: Critical Parameters. Note 2: Guaranteed by design, but not ...

Page 10

PIN FUNCTIONS “VCC” (PIN#1): 12V bias voltage input for internal circuit. Connecting a 1uF decoupling cap is recommended. “CX” (PIN#2): Charge-pump output internally clamped to 27V typical and 29V max. Connecting a 0.1uF / 50V cap to GND ...

Page 11

Voltage feedback input internally connected to the inverting input of the voltage error amplifier. “IREF” (PIN#16): Voltage error amplifier output also the current reference input to the current error amplifier clamped by ...

Page 12

Inverting input to the input current sense comparator. Connect it to the downstream of the input current sense resistor through a programming resistor. A constant current source flowing out of this pin goes through the programming resistor to ...

Page 13

SYSTEM THEORY OF OPERATION TM XPhase Voltage Regulator Architecture TM The XPhase architecture is designed for multiphase interleaved buck converters which are used in applications requiring small size, design flexibility, low voltage, high current and fast transient response. The architecture ...

Page 14

There is no unused or redundant silicon with the XPhase controller that can be configured for phase operation. PCB Layout is easier since the 5 wire bus eliminates the need for point−to−point wiring between the Control ...

Page 15

PWM Operation The PWM comparator is located in the Phase IC. Upon receiving a clock pulse, the PWM latch is set, the PWMRMP voltage begins to increase, the low side driver is turned off, and the high side driver is ...

Page 16

Loss-less inductor current sensing Inductor current can be sensed by connecting a series resistor and a capacitor network in parallel with the inductor and measuring the voltage across the capacitor. Figure 4 – Inductor Current Sensing and Current Sense Amplifier ...

Page 17

Control IC for voltage positioning and current limit protection Average Phase Current Share Loop Current sharing ...

Page 18

The limited voltage loop DC gain controls the voltage droop, Vdroop = ( Gv) Io, Where the voltage feedback divider factor current sense gain, and Gv is the voltage loop DC gain. The average ...

Page 19

IR3510 BLOCK DIAGRAM VCC Charge Pump 0.9V 27v OFF 10K ENABLE - ENABLE + 0.6V 1.2V COMPARATOR2 ENABLE COMPARATOR1 20uA 3K ICS- ICS+ 12.4V OC REGULATOR SEVERE OC COMPARATOR + 36K - GATE_I OFF - 10K + ...

Page 20

IR3510 THEORY OF OPERATION Vbias Regulator The Vbias regulator supplies a 6.8V/20mA bias voltage for internal circuitry, and through VBIAS pin it also provides reference voltage for Phase IC. Since the oscillator ramp amplitude tracks the VBIAS voltage, it should ...

Page 21

Input current limit Input current limit is required for hot-swap application to eliminate the inrush current drawn from the VIN power supply. There are two stages of input current limit. The first stage is input current limit, in which the ...

Page 22

Figure 9 depicts the start-up sequence of the voltage regulator. If there is no fault, the SS pin will start charging when the enable crosses the threshold. The current error amplifier output EAOUT is clamped low until SS reaches 1.35V. ...

Page 23

VREF Buffer The “VSET” pin inputs the VSET voltage from the system, and it is connected to the input of the VREF buffer. The buffered VSET voltage, VREF, is used as the reference voltage of the voltage error amplifier to ...

Page 24

Current Error Amplifier The voltage error amplifier output, IREF, is connected to the non-inverting input of the current error amplifier. The current report output, IO, is connected to the “IFB” pin through a feedback resistor, and then connected to the ...

Page 25

Under Voltage Lock Out There are two UVLOs, UVLO1 for Vcc and UVLO2 for P12V which is the voltage after the input FET. The UVLO1 for Vcc has the start threshold of 9V and stop threshold of 8.2V. It controls ...

Page 26

IN Enable P12V UVLO2 Vss EAOUT Vout VRRDY ORING Iout Open Remote Sense Line Protection If either remote sense line VOSEN+ or VOSEN- or both are open, the output of remote sense amplifier (VO) drops. The open-sense comparator monitors ...

Page 27

IR3510 DESIGN PROCEDURES Application Circuit Fig. 15 shows an application circuit with 4 phases using IR3088A as phase IC. Although It is not necessary to use one ORing FET for each phase recommended improve ...

Page 28

VCC,CX and VBIAS Caps Both VCC and VBIAS require a 0.1 uF 16V 0603 cap. For Charge Pump output cap CX, a 0.1uF 50V 0603 cap is needed since the charge pump voltage can 27V. Oscillator Resistor ...

Page 29

Tor The VRRDY goes HIGH when the soft-start cap voltage reaches the charge-up comparator threshold, which is 3.7V. The total soft-start time from Enable going HIGH to VRRDY going HIGH is determined by, Tos The soft-start cap can be selected ...

Page 30

In order to eliminate the inductor from the voltage loop, the current loop cross-over frequency needs to be much higher than the L-C resonant frequency. Meanwhile, it has to be less than 1/5 of the switching frequency. So, the current ...

Page 31

Rdrp = where, Iomax is the rated maximum output current Rfb is the resistor connected to the inverting input of the voltage error amplifier Vdrp is the required droop voltage at rated maximum output current. Current Report Gain and Thermal ...

Page 32

Rorset Where, Iormax is the max. allowed reverse current which is normally 10% or less of the rated output current. The constant current source Iorset is the same as Irosc which is determined by the switching frequency. Fig17. 15 shows ...

Page 33

PCB METAL AND COMPONENT PLACEMENT • Lead land width should be equal to nominal part lead width. The minimum lead to lead spacing should be ≥ 0.2mm to minimize shorting. • Lead land length should be equal to maximum part ...

Page 34

SOLDER RESIST • The solder resist should be pulled away from the metal lead lands by a minimum of 0.06mm. The solder resist mis-alignment is a maximum of 0.05mm and it is recommended that the lead lands are all Non ...

Page 35

STENCIL DESIGN • The stencil apertures for the lead lands should be approximately 80% of the area of the lead lands. Reducing the amount of solder deposited will minimize the occurrence of lead shorts. Since for 0.5mm pitch devices the ...

Page 36

PACKAGE INFORMATION 32L MLPQ ( Body) – θ IR WORLD HEADQUARTERS: 233 Kansas St., El Segundo, California 90245, USA Tel: (310) 252-7105 www.irf.com Page 24.4 C/W, θ =0. Data and ...