PM6670S STMicroelectronics, PM6670S Datasheet

PM6670S

Specifications of PM6670S

Available stocks

Related parts for PM6670S

PM6670S Summary of contents

Page 1

... SSTL18, SSTL15 and HSTL bus termination February 2010 VFQFPN-24 4x4 Description The device PM6670S is a complete DDR2/3 power supply regulator designed to meet JEDEC specifications. It integrates a constant on-time (COT) buck controller Apk sink/source low drop out regulator and low noise buffered reference ...

Page 2

... Current sensing and current limit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31 POR, UVLO and soft-start . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32 Power Good signal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33 VDDQ output discharge . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34 Gate drivers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35 Reference voltage and bandgap . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35 Over voltage and under voltage protections . . . . . . . . . . . . . . . . . . . . . 36 Device thermal protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36 VTT and VTTREF Soft-Start . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37 VTTREF and VTT outputs discharge . . . . . . . . . . . . . . . . . . . . . . . . . . . 37 Doc ID 14432 Rev 4 PM6670S ...

Page 3

... PM6670S 7.3 S3 and S5 power management pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38 8 Application information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39 8.1 External components selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39 8.1.1 8.1.2 8.1.3 8.1.4 8.1.5 8.1.6 8.1.7 9 Package mechanical data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51 10 Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53 Inductor selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41 Input capacitor selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42 Output capacitor selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43 MOSFETs selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44 Diode selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46 VDDQ current limit setting . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47 All ceramic capacitors application ...

Page 4

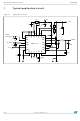

... Application circuit VDDQ ( LDO input IN4 23 4 VTTREF 2 C OUT3 24 VTT 1 C OUT2 4/54 + IN3 IN2 MODE HGATE 20 LDOIN PHASE 17 VTTREF LGATE PM6670S 19 VTTSNS CSNS 16 VTT PGND 9 VTTGND VSNS BYP Doc ID 14432 Rev BOOT L R LIM C PM6670S VIN VDDQ C OUT INT ...

Page 5

... PM6670S 2 Pin settings 2.1 Connections Figure 2. Pin connection (through top view VTTGND VTTGND VTTSNS VTTSNS DDRSEL DDRSEL PM6670 PM6670 VTTREF VTTREF SGND SGND AVCC AVCC Doc ID 14432 Rev 4 Pin settings VCC VCC LGATE LGATE PGND PGND 5/54 ...

Page 6

... S3 pin can't be left floating. Power Good signal (open drain output). High when VDDQ output voltage is within ± nominal value. Power ground for the switching section. Low-side gate driver output. Doc ID 14432 Rev 4 PM6670S Function 30. Section 7.1.4: Mode-of-operation 30. Section 7.1.8: VDDQ output discharge Section 7 ...

Page 7

... PM6670S Table 2. Pin functions (continued) N° Pin 18 VCC 19 CSNS 20 PHASE 21 HGATE 22 BOOT 23 LDOIN 24 VTT +5 V low-side gate driver supply. Bypass with a 100 nF capacitor to PGND. Current sense input for the switching section. This pin must be connected through a resistor to the drain of the synchronous rectifier (R set the current limit threshold ...

Page 8

... VTTREF, VREF, VTT, VTTSNS to SGND LDOIN, VTT, VTTREF, LDOIN to VTTGND Power dissipation @ °C A Parameter Thermal resistance junction to ambient Storage temperature range Operating ambient temperature range Junction operating temperature range Doc ID 14432 Rev 4 PM6670S Value Unit -0 -0 -0.3 to 0 ...

Page 9

... PM6670S 3.3 Recommended operating conditions Table 5. Recommended operating conditions Symbol V Input voltage range supply voltage AVCC V IC supply voltage VCC Parameter Doc ID 14432 Rev 4 Electrical data Values Unit Min Typ Max 4 4.5 - 5.5 V 4.5 - 5.5 9/54 ...

Page 10

... S3 and S5 tied to SGND. Discharge mode active. VCC connected to AVCC MODE and VOSC = 300 mV DDRSEL high, VOSC = 500 VSNS 4.5 V < V < -50 μA< I < 50 μA VREF Doc ID 14432 Rev 4 PM6670S Values Unit Min Typ Max 0 0.6 1 μ 4.1 4.25 4.4 V 3.85 4.0 4 ...

Page 11

... PM6670S Table 6. Electrical characteristics (continued) Symbol Parameter VDDQ output VDDQ output voltage, DDR3 V VDDQ VDDQ output voltage, DDR2 Feedback accuracy Current limit and zero crossing comparator I CSNS input bias current CSNS Comparator offset Positive current limit threshold Fixed negative current limit ...

Page 12

... VSNS VTTSNS VSNS VTT VSNS VTT MODE = DDRSEL = + S5 VTT MODE = +5 V, DDRSEL = MODE = + < I < VTT MODE = + < I < VTT MODE = + < I < VTT Doc ID 14432 Rev 4 PM6670S Values Unit Min Typ Max Ω 1.5 2 kΩ 0.2 0.4 0 μ -10 10 0.9 V 0.75 -20 ...

Page 13

... PM6670S Table 6. Electrical characteristics (continued) Symbol Parameter LDO source current limit I VTT,CL LDO sink current limit VTTREF section VTTREF output voltage V VTTREF output voltage VTTREF accuracy respect to VSNS/2 I VTTREF current limit VTTREF Power management section Turn OFF level S3,S5 Turn ON level ...

Page 14

... Input voltage (V) Input voltage (V) VDDQ line regulation, 1 Forced PWM Forced PWM No-Audible P-S No-Audible P-S Pulse-Skip Pulse-Skip 5.0 5.0 10.0 10.0 15.0 15.0 20.0 20.0 25.0 25.0 Input voltage (V) Input voltage (V) PM6670S 10 10 30.0 30.0 30.0 30.0 ...

Page 15

... PM6670S Figure 9. VDDQ load regulation, 1 1.860 1.860 1.850 1.850 1.840 1.840 1.830 1.830 1.820 1.820 1.810 1.810 1.800 1.800 0.001 0.001 0.01 0.01 0.1 0.1 Output current (A) Output current (A) Figure 11. VTT load regulation, 0.9 V, LDOIN = 1.8 V 0.940 0.930 0.920 0.910 0.900 ...

Page 16

... Typical operating characteristics Figure 15. Power-up sequence - AVCC above UVLO Figure 17. -1 1.8 A VTT load transient, 0.9 V 16/54 Figure 16. VDDQ soft-start, 1.8 V, heavy load Figure 18 VTTREF load transient, 0.9 V Doc ID 14432 Rev 4 PM6670S ...

Page 17

... PM6670S Figure 19. Non-tracking (soft) discharge Figure 21 VDDQ load transient, PWM Typical operating characteristics Figure 20. Tracking (fast) discharge, LDOIN = VDDQ Figure 22 VDDQ load transient, PWM Doc ID 14432 Rev 4 17/54 ...

Page 18

... Typical operating characteristics Figure 23 VDDQ load transient, pulse-skip Figure 25. Over-voltage protection, VDDQ = 1.8 V 18/54 Figure 24 VDDQ load transient, pulse-skip Figure 26. Under-voltage protection, VDDQ = 1.8 V Doc ID 14432 Rev 4 PM6670S ...

Page 19

... PM6670S 6 Block diagram Figure 27. Functional and block diagram VTTSNS VTTSNS LDOIN LDOIN VTT VTT VTTGND VTTGND VTTREF VTTREF SGND SGND AVCC AVCC DDRSEL DDRSEL DSCG DSCG Table 7. Legend SWEN Switching controller enable TD Tracking discharge enable NTD Non-tracking discharge enable BEN VTTREF buffer enable ...

Page 20

... Device description 7 Device description The PM6670SS is designed to satisfy DDR2-3 power supply requirements combining a synchronous buck controller buffered reference and a high-current low-drop out (LDO) linear regulator capable of sourcing and sinking Apk. The switching controller section is a high-performance, pseudo-fixed frequency, constant-on-time (COT) based regulator specifically designed for handling fast load transient over a wide range of input voltages ...

Page 21

... VDDQ section - constant on-time PWM controller The PM6670S uses a pseudo-fixed frequency, constant on-time (COT) controller as the core of the switching section well known that the COT controller uses a relatively simple algorithm and uses the ripple voltage derived across the output capacitor’s ESR to trigger the on-time one-shot generator. In this way, the output capacitor’ ...

Page 22

... MOSFETs' on-resistance and inductor's DCR) introduce voltage drops responsible for slight dependence on load current. In addition, the internal delay is due to a small dependence on input voltage. The PM6670S switching frequency can be set by an external divider connected to the VOSC pin. ...

Page 23

... Figure 30 shows the simplified block diagram of the constant-on-time controller. The switching regulator of the PM6670S owns a one-shot generator that ignites the high- side MOSFET when the following conditions are simultaneously satisfied: the PWM comparator is high (i.e. output voltage is lower than Vr = 0.9 V), the synchronous rectifier current is below the current limit threshold and the minimum off-time has expired ...

Page 24

... Thus, the voltage ripple on the output ) as shown in Figure 31 . INT ΔV t COMP C C FILT FILT Δ INT INT INT INT R R INT INT t VSNS ESR ESR C C OUT OUT Doc ID 14432 Rev 4 PM6670S REF REF I=g (V -Vr PWM Comparator Fb1 Fb1 Fb2 Fb2 ...

Page 25

... PM6670S The design of the external feedback network depends on the output voltage ripple. If the ripple is higher than approximately 20 mV, the correct CINT capacitor is usually enough to keep the loop stable. The stability of the system depends firstly on the output capacitor zero frequency. The following condition must be satisfied: Equation 6 where fixed design parameter (k > ...

Page 26

... In order to ensure stability it must be verified INT g > INT ⋅ π ⋅ π out Doc ID 14432 Rev REF REF I=g (V -Vr PWM PWM Comparator Comparator FILT FILT + R R Fb1 Fb1 Fb2 Fb2 − ESR is the total ripple at the T node, chosen Vr ⋅ Vout ⋅ R TOT PM6670S ...

Page 27

... PM6670S Equation 14 Moreover, the C INT Equation 15 where R is the sum of the ESR of the output capacitor and the equivalent ESR given by TOT the Virtual-ESR Network (R determines the minimum integrator capacitor value C Equation 16 The capacitor of the virtual-ESR Network chosen as follows: Equation 17 and R is calculated to provide the desired triangular ripple voltage: ...

Page 28

... Pulse-skip and no-audible pulse-skip modes High efficiency at light load conditions is achieved by PM6670S entering the pulse-skip mode (if enabled). When one of the two fixed output voltages is set, pulse-skip power saving is a default feature. At light load conditions the zero-crossing comparator truncates the low- side switch on-time as soon as the inductor current becomes negative ...

Page 29

... Some audio-noise sensitive applications cannot accept the switching frequency to enter the audible range as is possible in pulse-skip mode with very light loads. For this reason, the PM6670S implements an additional feature to maintain a minimum switching frequency of 33 kHz despite a slight efficiency loss. At very light load conditions, if any switching cycle has taken place within 30 μ ...

Page 30

... The MODE pin is used to firstly decide between fixed preset or adjustable (user defined) output voltages. When the MODE pin is connected the PM6670S allows setting the VDDQ voltage to 1 1.5 V just forcing the DDRSEL multilevel pin ground respectively (see Figure 35 a) ...

Page 31

... MODE 7.1.5 Current sensing and current limit The PM6670S switching controller uses a valley current sensing algorithm to properly handle the current limit protection and the inductor current zero-crossing information. The current is sensed during the conduction time of the low-side MOSFET. The current sensing element is the on-resistance of the low-side switch ...

Page 32

... DC output current plus half of the inductor ripple current: Equation 22 The PM6670S provides also a fixed negative current limit to prevent excessive reverse inductor current when the switching section sinks current from the load in forced-PWM (3 quadrant working conditions). This negative current limit threshold is measured between PHASE and PGND pins, comparing the drop magnitude on PHASE pin with an internal 110 mV fixed threshold ...

Page 33

... PM6670S After a fixed 3 ms total time, the soft-start finishes and UVP is released: if the output voltage doesn't reach the under voltage threshold within soft-start duration, the UVP condition is detected and the device performs a soft end and latches off. Depending on the load conditions, the inductor current may or may not reach the nominal value of the current limit during the soft-start ( Figure 38 ...

Page 34

... S5 tied to GND) and DSCG pin has been properly set. Figure 39. DSCG pin connection for discharge mode selection The PM6670S allows the user to choose between fast discharge (tracking discharge), soft discharge (non-tracking discharge discharge modes. Voltage on DSCG multilevel pin determines discharge mode as shown in Table 9 ...

Page 35

... PHASE pins work respectively as supply and return path for the high-side driver, while the low-side driver is directly fed through VCC and PGND pins. An important feature of the PM6670S gate drivers is the adaptive anti-cross-conduction circuitry, which prevents high-side and low-side MOSFETs from being turned on at the same time ...

Page 36

... Device thermal protection The internal control circuitry of the PM6670S self-monitors the junction temperature and turns all outputs off when the 150 °C limit has been overrun. This event causes the switching section to be immediately disabled and both switches to be opened. The controller enters in Soft-End Mode and the output is eventually kept to ground, turning the low side MOSFET on when the voltage is lower than 400 mV ...

Page 37

... At the same time the LDO drains constant current from LDOIN and keeps VTT in track with VTTREF that, in turn, is half the voltage at the VSNS pin. When the VDDQ output reaches 400 mV, the PM6670S switches on the internal discharge MOSFETs to complete the process (see In soft discharge (i ...

Page 38

... S5 system states by connecting S3-S5 pins to their respective sleep-mode signals in the notebook motherboard. Keeping S3 and S5 high, the S0 (Full-On) state is decoded and the outputs are alive state ( 0), the PM6670S maintains VDDQ and VTTREF outputs active and VTT output in high-impedance as needed. In S4/S5 states ( all outputs are turned off and, according to DSCG pin voltage, the proper Soft-End is performed ...

Page 39

... The following paragraphs will guide the user into a step-by-step design. 8.1 External components selection The PM6670S uses a pseudo-fixed frequency, constant on-time (COT) controller as the core of the switching section. The switching frequency can be set by connecting an external divider to the VOSC pin. The voltage seen at this pin must be greater than 0.8 V and lower than order to ensure system's linearity ...

Page 40

... R1 (kΩ) 330 330 330 330 330 330 40/54 V α = OSC OSC α = SNS OUT V OUT α ⋅ OSC OSC 1 2 OSC R2 (kΩ) Approx switching frequency (kHz Doc ID 14432 Rev 4 PM6670S ), the final Figure 29 250 300 350 400 450 500 ...

Page 41

... PM6670S 8.1.1 Inductor selection Once the switching frequency has been defined, the inductance value depends on the desired inductor ripple current. Low inductance value means great ripple current that brings poor efficiency and great output noise. On the other hand a great current ripple is desirable for fast transient response when a load step is applied ...

Page 42

... I I Cin LOAD RMS = ⋅ ESR I (max) loss Cin CinRMS Doc ID 14432 Rev 4 not only in case of hard L,PEAK +40 °C rms -30 % saturation current (A) current (A) 13.4 12 16.0 1 − + ⋅ Δ ⋅ − ⋅ ⋅ 2 ESR (max)) Cin LOAD CINRMS PM6670S 21.0 24 25.4 (max). ...

Page 43

... PM6670S It must be taken into account that in some MLCC the capacitance decreases when the operating voltage is near the rated voltage. In applications are listed. Table 14. Evaluated MLCC for input filtering Manufacturer TAIYO YUDEN UMK325BJ106KM-T TAIYO YUDEN GMK316F106ZL-T TAIYO YUDEN GMK325F106ZH-T TAIYO YUDEN GMK325BJ106KN ...

Page 44

... Series (μF) 4TPE220MF 220 4TPE150MI 220 4TPC220M 220 TNCB OE227MTRYF 220 = P P DHighSide conduction V = ⋅ OUT P R conduction DSon V IN Doc ID 14432 Rev MAX − the output I Rated voltage ESR max @100 kHz (V) (mΩ 2. switching ⋅ LOAD , MAX . min PM6670S ...

Page 45

... PM6670S where R is the drain-source on-resistance of the control MOSFET. DSon Switching losses are approximately given by: Equation 41 P switching where t and t ON OFF gate-driver current capability and the gate charge Q low R . Unfortunately low R DSon As general rule, the R MOSFET. Logic-level MOSFETs are recommended, as long as low-side and high-side gate drivers are ...

Page 46

... Type Gate charge (nC) DSon 25 IRF7313 46 shows some evaluated diodes. Table 19 Forward Rated reverse Type voltage (V) 0.34 0.34 Doc ID 14432 Rev Rated reverse voltage ( 0.069 30 0.011 30 0.054 30 Rated reverse voltage ( and a minimum recovery INmax Reverse current (μA) voltage (V) 30 0.00039 30 0.00039 PM6670S ...

Page 47

... PM6670S 8.1.6 VDDQ current limit setting The valley current limit is set by R current. The valley of the inductor current I Equation 45 The output current limit depends on the current ripple as shown in Figure 41. Valley current limit waveforms Current MAX LOAD 1 As the valley threshold is fixed, the greater the current ripple, the greater the DC output current will be ...

Page 48

... INT Ton One-shot generator + PWM Comparator - VREF + Integrator C R INT INT > ⋅ Zout ⋅ π INT g > INT ⎛ f ⋅ π − ⎜ Zout ⎝ k Doc ID 14432 Rev 4 VSNS Vr=0 out out Vref ⋅ ⎞ Vo ⎟ ⎠ PM6670S VDDQ ...

Page 49

... PM6670S If the ripple on pin COMP is greater than the integrator output dynamic (150 mV), an additional capacitor C attenuation factor of the output ripple, select: Equation 50 In order to reduce noise on pin COMP, it's possible to introduce a resistor R with C and C INT filt greater (10 or more times) than the switching frequency of the section: ...

Page 50

... ESR. A good trade-off is to consider an VESR equivalent ESR of 30-50 mΩ, even though the choice depends on inductor current ripple. Then choose R1 as follows: Equation 54 50/54 > ⋅ INT ⋅ VESR ⎛ ⎞ 1 ⎜ ⎜ ⎟ ⎟ ⋅ R π ⎝ ⎠ − R π Doc ID 14432 Rev 4 PM6670S ...

Page 51

... PM6670S 9 Package mechanical data In order to meet environmental requirements, ST offers these devices in different grades of ® ECOPACK packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions and product status are available at: www.st.com. ECOPACK trademark. Table 20. VFQFPN- mechanical data Dim θ mm. Min Typ ...

Page 52

... Package mechanical data Figure 44. Package dimensions 52/54 Doc ID 14432 Rev 4 PM6670S ...

Page 53

... PM6670S 10 Revision history Table 21. Document revision history Date 06-Feb-2008 23-Feb-2009 30-Oct-2009 03-Feb-2010 Revision 1 Initial release 2 Updated Table 3 on page 8 3 Updated package drawing in cover page, Updated Table 2 on page 4 21, Figure 30 on page 23 Doc ID 14432 Rev 4 Revision history Changes Table 20 on page 51 ...

Page 54

... Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America 54/54 Please Read Carefully: © 2010 STMicroelectronics - All rights reserved STMicroelectronics group of companies www.st.com Doc ID 14432 Rev 4 PM6670S ...