ISL6532CCR-T Intersil, ISL6532CCR-T Datasheet

ISL6532CCR-T

Specifications of ISL6532CCR-T

Related parts for ISL6532CCR-T

ISL6532CCR-T Summary of contents

Page 1

... PART NUMBER 17 GNDA ISL6532CCR 16 COMP ISL6532CCRZ (See Note *Add “-T” suffix to part number for tape and reel packaging. NOTE: Intersil Pb-free products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate termination finish, which is compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J Std-020B ...

Page 2

Block Diagram P5VSBY VDDQ S3 REGULATOR + - VDDQ(3) VTTSNS VTT REG - VTT(2) + GNDQ DISABLE { R U VREF_IN { GNDA + - UV/OV2 VREF_OUT S3# S5# 5VSBY VOLTAGE REFERENCE 0.800V 0.680V (-15%) 5V ...

Page 3

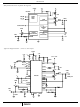

Simplified Power System Diagram SLP_S3 SLP_S5 5VSBY/3V3SBY V DDQ Q3 V AGP + Typical Application - 5V or 3.3V Input +3.3V PGOOD V DDQ SLP_S3 SLP_S5 V REF VTT_OUT V DDQ Q3 V AGP 1.5V + ...

Page 4

Typical Application - Input From 5V Dual +3.3V PGOOD V DDQ SLP_S3 SLP_S5 V REF VTT_OUT V DDQ Q3 V AGP 1. OUT2 4 ISL6532C 5VSBY +12V C BP S3# NCH S5# VREF_OUT OCSET ...

Page 5

Absolute Maximum Ratings 5VSBY, P5VSBY . . . . . . . . . . . . . . . . . . . . . . . . . GND - 0.3V to +7V P12V . . . . ...

Page 6

Electrical Specifications Recommended Operating Conditions, Unless Otherwise Noted. Refer to Block and Simplified Power System Diagrams and Typical Application Schematics (Continued) PARAMETER PWM CONTROLLER GATE DRIVERS UGATE and LGATE Source UGATE and LGATE Sink NCH BACKFEED CONTROL NCH Current Sink ...

Page 7

Functional Pin Description 5VSBY (Pin 2) 5VSBY is the bias supply of the ISL6532C typically connected to the 5V standby rail of an ATX power supply. During S4/S5 sleep states the ISL6532C enters a reduced power mode and ...

Page 8

NCH (Pin 22) NCH is an open-drain output that controls the MOSFET blocking backfeed from V to the input rail during sleep DDQ states. A 2kΩ or larger resistor tied between the 12V rail and the NCH ...

Page 9

Figure 1 shows the soft start sequence for a typical cold start. Due to the soft start capacitance, C VREF_IN pin, the transition profile of the V will have a more rounded features at the start and ...

Page 10

Had the cause of the over current still been present after the delay interval, the over current condition would be sensed and the regulator would be shut down again for another delay interval of three soft start cycles. The resulting ...

Page 11

Application Guidelines Layout Considerations Layout is very important in high frequency switching converter design. With power devices switching efficiently at 250kHz, the resulting current transitions from one device to another cause voltage spikes across the interconnecting impedances and parasitic circuit ...

Page 12

The PWM wave is smoothed by the output filter (L DRIVER OSC PWM COMPARATOR - DRIVER ∆V + OSC E REFERENCE ERROR AMP DETAILED COMPENSATION COMPONENTS ...

Page 13

ISL6532C 0.8V REFERENCE 650Ω DRIVE2 + - OUTPUT IMPEDANCE C 25 FB2 R 9 × 0 ------ - AGP FIGURE 7. COMPENSATION AND OUTPUT VOLTAGE SELECTION ...

Page 14

The ripple voltage and current are approximated by the following equations OUT OUT ∆I = ∆V x OUT ...

Page 15

MOSFET Selection - AGP LDO The main criteria for selection of the linear regulator pass transistor is package selection for efficient removal of heat. Select a package and heatsink that maintains the junction temperature below the rating with a maximum ...

Page 16

... Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use ...