ISL6530CBZ-T Intersil, ISL6530CBZ-T Datasheet

ISL6530CBZ-T

Specifications of ISL6530CBZ-T

Related parts for ISL6530CBZ-T

ISL6530CBZ-T Summary of contents

Page 1

... DDQ DS(ON) MOSFET which eliminates the need for a current sensing resistor. Ordering Information TEMP o PART NUMBER RANGE( C) PACKAGE ISL6530CB Lead SOIC ISL6530CBZ Lead SOIC (See Note) (Pb-free) ISL6530CR Lead 5x5 QFN ISL6530CRZ Lead 5x5 QFN (See Note) (Pb-free) ISL6530EVAL1, 2 Evaluation Board * Add “ ...

Page 2

Pinouts 24 LEAD (SOIC) TOP VIEW 24 UGATE1 1 23 BOOT1 2 22 PHASE1 3 21 VREF 4 20 FB1 COMP1 18 7 SENSE1 17 VREF_IN GNDA 15 PHASE2 BOOT2 13 ...

Page 3

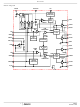

Block Diagram PGOOD FB1 COMP1 SENSE1 VREF_IN + VREF - FB2 COMP2 SENSE2 V2_SD 3 ISL6530 OCSET/SD VCC POWER-ON RESET (POR) + SOFT- - 40µA START OVER- CURRENT PWM ERROR COMPARATOR AMP INHIBIT + + - - PWM 0.8V REFERENCE ...

Page 4

Typical Application +5V R OCSET OCSET/SD RESET GNDA SLEEP V2_SD VREF_IN V REF (.5xV ) DDQ VREF COMP1 FB1 R FB1 SENSE1 4 ISL6530 PGOOD VCC PGOOD BOOT1 UGATE1 PHASE1 PVCC1 LGATE1 PGND1 ISL6530 BOOT2 UGATE2 PHASE2 LGATE2 PGND2 COMP2 ...

Page 5

Absolute Maximum Ratings Supply Voltage +7.0V CC ...

Page 6

Functional Pin Description 24 LEAD (SOIC) TOP VIEW 24 UGATE1 1 23 BOOT1 2 22 PHASE1 3 21 VREF 4 20 FB1 COMP1 18 7 SENSE1 17 VREF_IN GNDA 15 PHASE2 ...

Page 7

While the V supply “floats” held to about 50 via a low current window regulator which drives V DDQ via the SENSE2 pin. The window regulator can overcome least ±10mA of leakage ...

Page 8

TIME FIGURE 2. SOFT-START INTERVAL Shoot-Through Protection A shoot-through condition occurs when both the upper MOSFET and lower MOSFET are turned on simultaneously, effectively shorting the input voltage to ground. To protect the regulators from ...

Page 9

One method that may be employed to bypass the internal V reference generation is to supply an external reference TT directly to the V pin. When doing this the SENSE1 pin REF_IN must remain unconnected. Caution must be exercised when ...

Page 10

To avoid over-current tripping in the DS(ON) normal operating load range, find the R the equation above with: 1. The maximum r at the highest junction temperature. DS(ON) 2. The minimum I from the specification table. OCSET > ...

Page 11

Use copper filled polygons on the top and bottom circuit layers for the phase nodes. Use the remaining printed circuit layers for small signal wiring. The wiring traces from the GATE pins to the MOSFET gates should be kept ...

Page 12

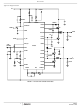

DRIVER OSC PWM COMPARATOR - DRIVER DV + OSC E REFERENCE ERROR AMP DETAILED COMPENSATION COMPONENTS COMP ISL6530 REFERENCE FIGURE 8. VOLTAGE-MODE ...

Page 13

Output Inductor Selection The output inductor is selected to meet the output voltage ripple requirements and minimize the converter’s response time to the load transient. The inductor value determines the converter’s ripple current and the ripple voltage is a function ...

Page 14

Ensure that both MOSFETs are within their maximum junction temperature at high ambient temperature by calculating the temperature rise according to package thermal-resistance specifications. A separate heatsink may be necessary depending upon MOSFET power, package type, ambient temperature and air ...

Page 15

ISL6530 DC-DC Converter Application Circuit Figure 11 shows an application circuit for a DDR SDRAM power supply, including V (+2.5V) and V DDQ Detailed information on the circuit, including a complete Bill- V2_SD PGOOD VREF VREF_IN C 30 100pF GNDA ...

Page 16

Small Outline Plastic Packages (SOIC) N INDEX 0.25(0.010) H AREA E - SEATING PLANE - -C- α µ 0.10(0.004) 0.25(0.010 NOTES: 1. Symbols are defined in ...

Page 17

... Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use ...