ISL6530CBZ-T Intersil, ISL6530CBZ-T Datasheet - Page 10

ISL6530CBZ-T

Manufacturer Part Number

ISL6530CBZ-T

Description

IC CONTROLLER INTEL 24SOIC

Manufacturer

Intersil

Datasheet

1.ISL6530CB-T.pdf

(17 pages)

Specifications of ISL6530CBZ-T

Applications

Controller, Intel Pentium® III, IV

Voltage - Input

4.5 ~ 5.5 V

Number Of Outputs

2

Voltage - Output

2.5V

Operating Temperature

0°C ~ 70°C

Mounting Type

Surface Mount

Package / Case

24-SOIC (7.5mm Width)

Peak Reflow Compatible (260 C)

Yes

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

ISL6530CBZ-TTR

r

normal operating load range, find the R

the equation above with:

For an equation for the ripple current see the section under

component guidelines titled Output Inductor Selection.

A small ceramic capacitor should be placed in parallel with

R

presence of switching noise on the input voltage.

Current Sinking

The ISL6530 V

through protection method which allows the converter to sink

current as well as source current. Care should be exercised

when designing a converter with the ISL6530 when it is

known that the converter may sink current.

When the converter is sinking current, it is behaving as a

boost converter that is regulating its input voltage. This

means that the converter is boosting current into the input

rail of the regulator. If there is nowhere for this current to go,

such as to other distributed loads on the rail or through a

voltage limiting protection device, the capacitance on this rail

will absorb the current. This situation will allow the voltage

level of the input rail to increase. If the voltage level of the rail

is boosted to a level that exceeds the maximum voltage

rating of any components attached to the input rail, then

those components may experience an irreversible failure or

experience stress that may shorten their lifespan. Ensuring

that there is a path for the current to flow other than the

capacitance on the rail will prevent this failure mode.

To insure that the current does not boost up the input rail

voltage of the V

input rail of the V

regulator. The current being sunk by the V

be fed into the V

SDRAM memory module and back into the V

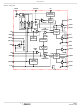

Figure 6 shows the recommended configuration and the

resulting current loop.

DS(ON)

1. The maximum r

2. The minimum I

3. Determine I

OCSET

where ∆I is the output inductor ripple current.

variations. To avoid over-current tripping in the

to smooth the voltage across R

TT

TT

PEAK

DDQ

TT

regulator incorporates a MOSFET shoot-

regulator, it is recommended that the

DS(ON)

OCSET

regulator be the output of the V

rail and then drawn into the DDR

for

at the highest junction temperature.

from the specification table.

I

PEAK

10

>

I

OUT MAX

OCSET

OCSET

(

TT

TT

regulator will

)

+

resistor from

in the

(

--------- -

regulator.

∆I

2

)

DDQ

,

ISL6530

Application Guidelines

Layout Considerations

Layout is very important in high frequency switching

converter design. With power devices switching efficiently at

300kHz, the resulting current transitions from one device to

another cause voltage spikes across the interconnecting

impedances and parasitic circuit elements. These voltage

spikes can degrade efficiency, radiate noise into the circuit,

and lead to device overvoltage stress. Careful component

layout and printed circuit board design minimizes the voltage

spikes in the converters.

As an example, consider the turn-off transition of the PWM

MOSFET. Prior to turn-off, the MOSFET is carrying the full

load current. During turn-off, current stops flowing in the

MOSFET and is picked up by the lower MOSFET. Any

parasitic inductance in the switched current path generates a

large voltage spike during the switching interval. Careful

component selection, tight layout of the critical components,

and short, wide traces minimizes the magnitude of voltage

spikes.

There are two sets of critical components in a DC-DC

converter using the ISL6530. The switching components are

the most critical because they switch large amounts of

energy, and therefore tend to generate large amounts of

noise. Next are the small signal components which connect

to sensitive nodes or supply critical bypass current and

signal coupling.

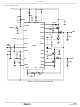

A multi-layer printed circuit board is recommended. Figure 7

shows the connections of the critical components in the

converter. Note that capacitors C

represent numerous physical capacitors. Dedicate one solid

layer, usually a middle layer of the PC board, for a ground

plane and make all critical component ground connections

with vias to this layer. Dedicate another solid layer as a

power plane and break this plane into smaller islands of

common voltage levels. Keep the metal runs from the

PHASE terminals to the output inductor short. The power

plane should support the input power and output power

ISL6530

UGATE1

PHASE1

UGATE2

PHASE2

LGATE1

LGATE2

FIGURE 6. V

+5V

TT

CURRENT SINKING LOOP

IN

V

and C

DDQ

V

TT

OUT

R

T

could each

November 15, 2004

V

REF

SDRAM

DDR

+

-

FN9052.2