ISL6539IAZ-T Intersil, ISL6539IAZ-T Datasheet

ISL6539IAZ-T

Specifications of ISL6539IAZ-T

Related parts for ISL6539IAZ-T

ISL6539IAZ-T Summary of contents

Page 1

... CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures. | 1-888-INTERSIL or 1-888-468-3774 Intersil (and design registered trademark of Intersil Americas Inc. Copyright Intersil Americas Inc. 2004-2006, 2007, 2010. All Rights Reserved All other trademarks mentioned are the property of their respective owners. ...

Page 2

... Ordering Information TEMP. PART PART RANGE NUMBER MARKING (°C) ISL6539IAZ* ISL 6539IAZ - QSOP (Note) ISL6539CAZ* ISL 6539CAZ - QSOP (Note) *Add “-T” suffix for tape and reel. Please refer to TB347 for details on reel specifications. NOTE: These Intersil Pb-free plastic packaged products employ ...

Page 3

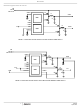

Generic Application Circuits V IN 3.3V OR 5.0V TO 15V 5V FIGURE 1. ISL6539 APPLICATION CIRCUIT FOR TWO CHANNEL POWER SUPPLY V IN 3.3V OR 5.0V TO 15V 5V VREF PG2/VREF FIGURE 2. ISL6539 APPLICATION CIRCUIT FOR COMPLETE DDR MEMORY ...

Page 4

... QSOP Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . Maximum Junction Temperature (Plastic Package +150°C Maximum Storage Temperature Range . . . . . . . . . .-65°C to +150°C Pb-free reflow profile . . . . . . . . . . . . . . . . . . . . . . . . . .see link below + 0.3V http://www.intersil.com/pbfree/Pb-FreeReflow.asp CC Recommended Operating Conditions Bias Voltage, VCC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +5.0V Input Voltage, VIN . . . . . . . . . . . . . . . . . . . . .+3.3V or 5.0V to +18.0V Ambient Temperature Range, Commercial . . . . . . . . . 0°C to +70°C Junction Temperature Range, Commercial . . . . . . . . 0° ...

Page 5

Electrical Specifications Recommended Operating Conditions, Unless Otherwise Noted. (Continued) PARAMETER PWM CONVERTERS Load Regulation VSEN Pin Bias Current Minimum Duty Cycle Maximum Duty Cycle Undervoltage Shut-Down Level Overvoltage Protection GATE DRIVERS Upper Drive Pull-Up Resistance Upper Drive Pull-Down Resistance Lower ...

Page 6

The anode of the bootstrap diode is connected to the VCC voltage. ISEN1, ISEN2 (Pin 7, 22) These pins are used to monitor the voltage drop across the lower MOSFET for current ...

Page 7

V IN CIN1 10µF LO1 V1 (2.5V) 4.7µH RFB11 17.8k CO13 CO11 220µF 4.7µF CFB1 0.01 F µ FDS6912A RFB12 10k CSOFT1 0.01µF FIGURE 3. TYPICAL APPLICATION CIRCUIT AS DUAL SWITCHER, VOUT1 = 2.5V, VOUT2 = 1.8V VIN CIN1 10µF ...

Page 8

Block Diagram BOOT1 UGATE1 PHASE1 ADAPTIVE DEAD-TIME DIODE EMULATION PGND1 V/I SAMPLE TIMING LGATE1 VCC 16.7pF 1MΩ 500kΩ 300kΩ VSEN1 - 1.25pF 4.4kΩ 0.9V ERROR AMP 1 REF SOFT1 ISEN1 140Ω - CURRENT SAMPLE CURRENT + SAMPLE OCSET1 ...

Page 9

Theory of Operation Operation The ISL6539 is a dual channel PWM controller intended for use in power supplies for graphic chipsets, SDRAM, DDR DRAM, or other power applications. The IC integrates two control circuits for two synchronous buck converters. The ...

Page 10

UGA ISEN Q2 LGA T E VOUT VSEN OCSET ISL6539 R OC FIGURE 6. THE INTERNAL COMPENSATOR Current Sensing The current on the lower MOSFET is sensed by measuring its voltage ...

Page 11

TABLE 1. PWM COMPARATOR RAMP AMPLITUDE FOR DUAL SWITCHER APPLICATION VIN PIN CONNECTIONS Ch1 and Ch2 Input Voltage Input voltage > 4.2V Input voltage < 4.2V GND TABLE 2. PWM COMPARATOR RAMP VOLTAGE AMPLITUDE FOR DDR APPLICATION VIN PIN CONNECTION ...

Page 12

R , output LC filter, and feedback network, the CS system loop gain can be accurately analyzed and modified by the system designers based on the applications requirements FILTER 30 20 COMPENSATOR 10 VO/VC 0 ...

Page 13

PGOOD 1 8 CLK IL 2 VOUT 3 Ch1 5.0V Ch2 100mV Ch3 1.0A Ω FIGURE 10. OVERCURRENT PROTECTION Due to the nature of the current sensing technique and to accommodate a wide range of the r DS(ON) value of ...

Page 14

DDR pin is set high. As the VTT channel tracks the VDDQ/2 voltage, the soft-start function is not required, and the SOFT2 pin may be left open, in the event both channels are enabled ...

Page 15

Sometimes, if the phase node is very noisy, a resistor can be put on the ISEN pin to ground. This resistor together with the R can divide the phase node voltage down, seen by the CS internal current sense amplifier, ...

Page 16

AC peak-to-peak current. These two voltages can be represented by Equations 21 and 22 ΔV = ---------------- - c 8Cf sw ΔV I ESR = esr P P – These two components constitute a ...

Page 17

The total power loss of the upper MOSFET is the sum of the switching loss and the conduction loss. The temperature rise on the MOSFET can be calculated based on the thermal impedance given on the datasheet of the MOSFET. ...

Page 18

Power Layers: Power Ground 4. Bottom Layer: Power MOSFET, Inductors and other Power traces good engineering practice to separate the power voltage and current flowing path from the control and logic level signal path. The controller ...

Page 19

Pin 14, VIN This pin connects to battery voltage, and is less noise sensitive. Copper Size for the Phase Node Big coppers on both sides of the Phase node introduce parasitic capacitance. The capacitance of PHASE should be kept very ...

Page 20

... Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use ...