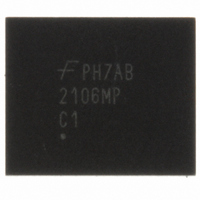

FAN2106MPX Fairchild Semiconductor, FAN2106MPX Datasheet - Page 10

FAN2106MPX

Manufacturer Part Number

FAN2106MPX

Description

IC BUCK SYNC ADJ 6A 25MLP

Manufacturer

Fairchild Semiconductor

Series

TinyBuck™r

Type

Step-Down (Buck)r

Datasheet

1.FAN2106MPX.pdf

(15 pages)

Specifications of FAN2106MPX

Internal Switch(s)

Yes

Synchronous Rectifier

Yes

Number Of Outputs

1

Voltage - Output

3 ~ 21 V

Current - Output

6A

Frequency - Switching

300kHz ~ 600kHz

Voltage - Input

3 ~ 24 V

Operating Temperature

-10°C ~ 85°C

Mounting Type

Surface Mount

Package / Case

25-MLP

Power - Output

2.8W

Mounting Style

SMD/SMT

Operating Temperature Range

- 10 C to + 85 C

Output Voltage

0.4 V to 3.2 V

Primary Input Voltage

24V

No. Of Outputs

1

Output Current

6A

No. Of Pins

25

Filter Terminals

SMD

Output Current Max

6A

Rohs Compliant

Yes

Input Voltage Primary Max

24V

For Use With

FEB167 - BOARD EVAL FOR FAN2106

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

FAN2106MPXTR

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

FAN2106MPX

Manufacturer:

FAIRCHILD/仙童

Quantity:

20 000

© 2009 Fairchild Semiconductor Corporation

FAN2106 • Rev. 1.1.0

Circuit Description

PWM Generation

Refer to Figure 2 for the PWM control mechanism.

FAN2106 uses the summing-mode method of control to

generate the PWM pulses. An amplified current-sense

signal is summed with an internally generated ramp and

the combined signal is compared with the output of the

error amplifier to generate the pulsewidth to drive the

high-side MOSFET. Sensed current from the previous

cycle is used to modulate the output of the summing

block. The output of the summing block is also

compared against a voltage threshold set by the R

resistor to limit the inductor current on a cycle-by-cycle

basis. The R

for the internal ramp and provides input voltage feed-

forward function. The controller facilitates external

compensation for enhanced flexibility.

Initialization

Once V

HIGH, the IC checks for a shorted FB pin before

releasing the internal soft-start ramp (SS).

If the parallel combination of R1 and R

internal SS ramp is not released and the regulator does

not start.

Enable

FAN2106 has an internal pull-up to the ENABLE (EN)

pin so that the IC is enabled once V

UVLO threshold. Connecting a small capacitor across

EN and AGND delays the rate of voltage rise on the EN

pin. The EN pin also serves for the restart whenever a

fault occurs (refer to the Auto-Restart section). If the

regulator is enabled externally, the external EN signal

should go HIGH only after V

applications where such sequencing is required,

FAN2106 can be enabled (after the V

external control, as shown in Figure 21.

Soft-Start

Once internal SS ramp has charged to 0.8V (T0.8), the

output voltage is in regulation. Until SS ramp reaches

1.0V (T1.0), the fault latch is inhibited.

To avoid skipping the soft-start cycle, it is necessary to

apply V

sequence for powering up would be VIN VCC EN.

Figure 21. Enabling with External Control

IN

CC

before V

exceeds the UVLO threshold and EN is

RAMP

resistor helps set the charging current

CC

reaches its UVLO threshold. Normal

3.3n

CC

14

is established. For

EN

FAN2106

CC

BIAS

CC

comes up) with

is ≤ 1KΩ, the

exceeds the

LIM

10

Soft-start time is a function of switching frequency.

Cycling V

and resets the IC. In applications where external EN

signal is used, V

before the EN signal comes up to prevent skipping the

soft-start function.

Startup on Pre-Bias

The regulator does not allow the low-side MOSFET to

operate in full synchronous rectification mode until

internal SS ramp reaches 95% of V

helps the regulator start on a pre-biased output and

ensures that the pre-biased outputs are not discharged

during soft-start.

Protections

The converter output is monitored and protected

against extreme overload, short-circuit, over-voltage,

under-voltage, and over-temperature conditions.

Under-Voltage Shutdown

If the voltage on the FB pin remains below the under-

voltage threshold for 16 consecutive clock cycles, the

fault latch is set and the converter shuts down. This

protection is not active until the internal SS ramp

reaches 1.0V during soft-start.

Over-Voltage Protection

If voltage on the FB pin exceeds 115% of V

consecutive clock cycles, the fault latch is set and

shutdown occurs.

A shorted high-side MOSFET condition is detected

when SW voltage exceeds ~0.7V while the low-side

EN

FB

SS

Figure 22. Soft-Start Timing Diagram

CC

or the EN pin discharges the internal SS

IN

1.35V

3200 CLKs

4000 CLKs

and V

2400 CLKs

1.0V

0.8V

CC

T0.8

should be established

T1.0

REF

(~0.76V). This

Fault

Latch

Enable

0.8V

www.fairchildsemi.com

REF

for two