L6726ATR STMicroelectronics, L6726ATR Datasheet - Page 22

L6726ATR

Manufacturer Part Number

L6726ATR

Description

IC CTRLR PWM SGL PHASE 8-SOIC

Manufacturer

STMicroelectronics

Type

Step-Down (Buck)r

Datasheet

1.L6726ATR.pdf

(35 pages)

Specifications of L6726ATR

Internal Switch(s)

No

Synchronous Rectifier

No

Number Of Outputs

1

Voltage - Output

Adj to 0.8V

Frequency - Switching

270kHz

Voltage - Input

1.5 ~ 12 V

Operating Temperature

-20°C ~ 85°C

Mounting Type

Surface Mount

Package / Case

8-SOIC (3.9mm Width)

Output Current

1.5 A

Input Voltage

4.1 V to 13.2 V

Operating Temperature Range

- 40 C to + 150 C

Mounting Style

SMD/SMT

For Use With

497-9046 - BOARD EVAL BASED ON L6726A497-6364 - BOARD DEMO FOR TS4995EIJT497-6259 - BOARD EVAL 1PH STPDN CONV L6726A

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Current - Output

-

Power - Output

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Other names

497-5906-2

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

L6726ATR

Manufacturer:

FUJI

Quantity:

130

Part Number:

L6726ATR

Manufacturer:

ST

Quantity:

20 000

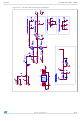

Application Information

9.2

9.3

22/35

Output capacitors

Output capacitors choice depends on the application constraints in point of output voltage

ripple and output voltage deviation during a load transient.

During steady-state conditions, the output voltage ripple is influenced by ESR and

capacitance of the output capacitors as follows:

Where ΔI

will be lower than the sum of their moduli. Even ESL and board parasitic inductance can

contribute significantly to output ripple.

During a load variation, the output capacitors supply to the load the additional current or

absorb the current in excess delivered by the inductor until converter reaction is completed.

In fact, even if the controller react immediately to the load transient saturating the duty cycle

to 80% or 0%, the current slew rate is limited by the inductance. At first approximation,

output voltage drop, based on ESR and capacitor charge/discharge and considering an

ideal load-step, can be estimated as follows:

Where ΔV

the load appliance or V

MLCC capacitors typically have low ESR to minimize the ripple but also have low

capacitance that do not minimize the capacitive voltage deviation during load transient. On

the contrary, electrolytic capacitors usually have higher capacitance to minimize capacitive

voltage deviation during load transient, but also higher ESR value resulting in higher ripple

voltage and resistive voltage drop. For these reasons, a mix between electrolytic and MLCC

capacitor is usually suggested to minimize ripple as well as reducing voltage deviation in

dynamic conditions.

Input capacitors

The input capacitor bank is designed mainly to stand input rms current, which depends on

output current (I

The equation reaches its maximum value, I

capacitor ESR:

ΔV

ΔV

ΔV

I

ΔV

P

rms

=

OUT_ESR

OUT_C

OUT_ESR

OUT_C

=

ESR I

I

OUT

L

=

=

L

⋅

is the inductor current ripple. These contribution are not in phase, so total ripple

=

ΔI

=

is the voltage applied to the inductor during the transient (

⋅

rms

------------------------------------- -

2 C

L

⋅

ΔI

ΔI

L ΔI

D

2

⋅

⋅

L

OUT

OUT

-------------------------------------- -

8 C

⋅

OUT

⋅

(

⋅

1 D

ESR

OUT

–

⋅

) and duty-cycle (D) for the regulation as follows:

OUT

⋅

ESR

ΔV

1

2

)

OUT

L

⋅

F

SW

for the load removal).

Doc ID 12754 Rev 4

OUT

/2, when D = 0.5. Losses depend on input

D

MAX

⋅

V

IN

–

V

OUT

L6726A

for