DS34S108GN+ Maxim Integrated Products, DS34S108GN+ Datasheet

DS34S108GN+

Specifications of DS34S108GN+

Related parts for DS34S108GN+

DS34S108GN+ Summary of contents

Page 1

... DS34S102GN 10/100 xMII DS34S102GN+ Ethernet Interface MAC DS34S104GN DS34S104GN+ Clock DS34S108GN Adapters DS34S108GN+ +Denotes lead(Pb)-free/RoHS-compliant package (explanation). Features 5 . Ordering Information PORTS TEMP RANGE PIN-PACKAGE 1 -40°C to +85°C 256 TECSBGA 1 -40°C to +85°C 256 TECSBGA 2 -40°C to +85°C 256 TECSBGA 2 -40° ...

Page 2

DS34S101, DS34S102, DS34S104, DS34S108 1 Applicable Standards Table 1-1. Applicable Standards SPECIFICATION IEEE Carrier Sense Multiple Access with Collision Detection (CSMA/CD) Access Method and IEEE 802.3 Physical Layer Specifications (2005) IEEE 1149.1 Standard Test Access Port and Boundary-Scan Architecture, ...

Page 3

DS34S101, DS34S102, DS34S104, DS34S108 2 Detailed Description The DS34S108 is an 8-port TDM-over-Packet (TDMoP) IC. The DS34S104, DS34S102 and DS34S101 have the same functionality as the DS34S108, except they have only ports, respectively. These sophisticated ...

Page 4

DS34S101, DS34S102, DS34S104, DS34S108 3 Application Examples In Figure 3-1, a DS34S10x device is used in each TDMoP gateway to map TDM services into a packet-switched metropolitan network. TDMoP data is carried over various media: fiber, wireless, G/EPON, coax, ...

Page 5

DS34S101, DS34S102, DS34S104, DS34S108 Figure 3-2. TDMoP in Cellular Backhaul Other Possible Applications Point-to-Multipoint TDM Connectivity over IP/Ethernet The DS34S10x devices support NxDS0 TDMoP connections (known as bundles) with or without CAS (Channel Associated Signaling). There is no need ...

Page 6

DS34S101, DS34S102, DS34S104, DS34S108 4 Block Diagram Figure 4-1. Top-Level Block Diagram TDMn_ACLK TDMn_TX TDMn_TCLK TDMn_TX_SYNC TDMn_TX_MF_CD TDMn_TSIG_CTS TDMn_RCLK TDMn_RX TDMn_RX_SYNC TDMn_RSIG_RTS Rev: 032609 CLAD1 38.88MHz 2.048/1.544MHz TDMoP Block all 8 ports Payload Type Clock SDRAM Machines Recovery Controller ...

Page 7

DS34S101, DS34S102, DS34S104, DS34S108 5 Features Global Features • TDMoP Interfaces DS34S101: 1 E1/T1/serial TDM interface o DS34S102: 2 E1/T1/serial TDM interfaces o DS34S104: 4 E1/T1/serial TDM interfaces o DS34S108: 8 E1/T1/serial TDM interfaces o All four devices: optionally ...

Page 8

DS34S101, DS34S102, DS34S104, DS34S108 TDMoP TDM Interfaces • Supports single high-speed E3 STS-1 interface on port 1 or one (DS34S101), two (DS34S102), four (DS34S104) or eight (DS34S108) E1 serial interfaces • For single high-speed E3, ...

Page 9

DS34S101, DS34S102, DS34S104, DS34S108 Automatic transition to holdover when link break is detected o TDMoP Delay Variation Compensation • Configurable jitter buffers compensate for delay variation introduce by the IP/MPLS/Ethernet network • Large maximum jitter buffer depths: E1: up ...

Page 10

DS34S101, DS34S102, DS34S104, DS34S108 7 Pin Descriptions 7.1 Short Pin Descriptions Table 7-1. Short Pin Descriptions PIN NAME TYPE TDM Interface TDMn_ACLK O TDMn_TCLK Ipu TDMn_TX O TDMn_TX_SYNC Ipd TDMn_TX_MF_CD IOpd TDMn_TSIG_CTS O TDMn_RCLK Ipu TDMn_RX Ipu TDMn_RX_SYNC Ipd ...

Page 11

DS34S101, DS34S102, DS34S104, DS34S108 PIN NAME TYPE H_WR_BE2_N / SPI_SEL_N H_WR_BE3_N / SPI_CI H_READY_N Oz H_INT O JTAG Interface JTRST_N Ipu JTCLK Ipd JTMS Ipu JTDI Ipu JTDO Oz Reset and Factory Test Pins RST_SYS_N Ipu HIZ_N SCEN Ipd ...

Page 12

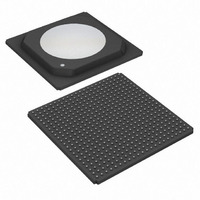

DS34S101, DS34S102, DS34S104, DS34S108 8 Package Information For the latest package outline information and land patterns DS34S101, DS34S102 and DS34S108 have a 256-lead thermally enhanced chip-scale ball grid array (TECSBGA) package. The TECSBGA package dimensions are shown ...

Page 13

... Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time 2009 Maxim Integrated Products DESCRIPTION preliminary release version. Maxim is a registered trademark of Maxim Integrated Products, Inc. PAGES CHANGED — 10, 15 ...