ISL6520EVAL1 Intersil, ISL6520EVAL1 Datasheet - Page 8

ISL6520EVAL1

Manufacturer Part Number

ISL6520EVAL1

Description

EVALUATION BOARD 1 ISL6520

Manufacturer

Intersil

Datasheet

1.ISL6520CBZ.pdf

(11 pages)

Specifications of ISL6520EVAL1

Mfg Application Notes

ISL6520(A) App Note

Main Purpose

DC/DC, Step Down

Outputs And Type

1, Non-Isolated

Voltage - Output

3.3V

Current - Output

15A

Voltage - Input

4.5 ~ 5.5V

Regulator Topology

Buck

Frequency - Switching

300kHz

Board Type

Fully Populated

Utilized Ic / Part

ISL6520

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Power - Output

-

the MOSFETs and between the drain of Q

of Q

The important parameters for the bulk input capacitor are the

voltage rating and the RMS current rating. For reliable

operation, select the bulk capacitor with voltage and current

ratings above the maximum input voltage and largest RMS

current required by the circuit. The capacitor voltage rating

should be at least 1.25 times greater than the maximum

input voltage and a voltage rating of 1.5 times is a

conservative guideline. The RMS current rating requirement

for the input capacitor of a buck regulator is approximately

1/2 the DC load current.

For a through hole design, several electrolytic capacitors

may be needed. For surface mount designs, solid tantalum

capacitors can be used, but caution must be exercised with

regard to the capacitor surge current rating. These

capacitors must be capable of handling the surge-current at

power-up. Some capacitor series available from reputable

manufacturers are surge current tested.

MOSFET Selection/Considerations

The ISL6520 requires two N-Channel power MOSFETs.

These should be selected based upon r

supply requirements, and thermal management

requirements.

In high-current applications, the MOSFET power

dissipation, package selection and heatsink are the

dominant design factors. The power dissipation includes

two loss components; conduction loss and switching loss.

The conduction losses are the largest component of power

dissipation for both the upper and the lower MOSFETs.

These losses are distributed between the two MOSFETs

according to duty factor (see the equations below). Only

the upper MOSFET has switching losses, since the lower

MOSFETs body diode or an external Schottky rectifier

across the lower MOSFET clamps the switching node

before the synchronous rectifier turns on. These equations

assume linear voltage-current transitions and do not

adequately model power loss due the reverse-recovery of

the lower MOSFET’s body diode. The gate-charge losses

are dissipated by the ISL6520 and don't heat the

MOSFETs. However, large gate-charge increases the

switching interval, t

switching losses. Ensure that both MOSFETs are within

their maximum junction temperature at high ambient

temperature by calculating the temperature rise according

to package thermal-resistance specifications. A separate

heatsink may be necessary depending upon MOSFET

power, package type, ambient temperature and air flow.

2

.

SW

which increases the upper MOSFET

8

DS(ON)

1

and the source

, gate

ISL6520

Given the reduced available gate bias voltage (5V),

logic-level or sub-logic-level transistors should be used for

both N-MOSFETs. Caution should be exercised with

devices exhibiting very low V

shoot-through protection present aboard the ISL6520 may

be circumvented by these MOSFETs if they have large

parasitic impedences and/or capacitances that would

inhibit the gate of the MOSFET from being discharged

below its threshold level before the complementary

MOSFET is turned on.

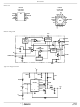

Figure 7 shows the upper gate drive (BOOT pin) supplied

by a bootstrap circuit from V

C

the PHASE pin. The supply is refreshed to a voltage of V

less the boot diode drop (V

MOSFET, Q

P

Where: D is the duty cycle = V

P

BOOT

LOWER

UPPER

+

-

ISL6520

+5V

VCC

, develops a floating supply voltage referenced to

t

F

SW

FIGURE 7. UPPER GATE DRIVE BOOTSTRAP

= Io

S

= Io

is the switching frequency.

is the switching interval, and

2

2

2

, turns on.

x r

x r

DS(ON)

DS(ON)

+ V

GND

D

BOOT

BOOT

UGATE

PHASE

LGATE

D

-

x D +

x (1 - D)

OUT

C

D

BOOT

CC

1

2

) each time the lower

GS(ON)

Io x V

/ V

. The boot capacitor,

IN

Q1

Q2

+5V

,

IN

characteristics. The

x t

SW

x F

NOTE:

V

NOTE:

V

G-S

G-S

S

≈

≈

V

V

April 3, 2007

CC

CC

FN9009.6

(EQ. 8)

-V

CC

D