ISL6530EVAL2 Intersil, ISL6530EVAL2 Datasheet - Page 7

ISL6530EVAL2

Manufacturer Part Number

ISL6530EVAL2

Description

EVALUATION BOARD 2 ISL6530

Manufacturer

Intersil

Datasheet

1.ISL6530CB-T.pdf

(17 pages)

Specifications of ISL6530EVAL2

Main Purpose

Special Purpose DC/DC, DDR Memory Supply

Outputs And Type

2, Non-Isolated

Power - Output

31.25W

Voltage - Output

2.5V, 1.25V

Current - Output

10A, 5A

Voltage - Input

4.5 ~ 5.5V

Regulator Topology

Buck

Frequency - Switching

300kHz

Board Type

Fully Populated

Utilized Ic / Part

ISL6530

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

While the V

V

via the SENSE2 pin. The window regulator can overcome up

to at least ±10mA of leakage on V

While V2_SD is high, PGOOD is low.

PHASE1 and PHASE2

Connect PHASE1 and PHASE2 to the corresponding upper

MOSFET source. This pin is used as part of the upper

MOSFET bootstrapped drives. PHASE1 is used to monitor

the voltage drop across the upper MOSFET of the V

regulator for over-current protection. The PHASE1 pin is

monitored by the adaptive shoot through protection circuitry

to determine when the upper FET of the V

turned off.

FB1, COMP1, FB2, and COMP2

COMP1, COMP2, FB1, and FB2 are the available external

pins of the error amplifiers. The FB1 and FB2 pins are the

inverting inputs of each error amplifier and the COMP1 and

COMP2 pins are the associated outputs. An appropriate AC

network across these pins is used to compensate the

voltage-controlled feedback loop of each converter.

VREF and VREF_IN

VREF produces a voltage equal to one half of the voltage on

SENSE1. This low current output is connected to the VREF

input of the DDRAM devices being powered. This same

voltage is used as the reference input of the V

amplifier. Thus V

VREF_IN is used as an option to overdrive the internal

resistor divider network that sets the voltage for both

VREF_OUT and the reference voltage for the V

100pF capacitor between VREF_IN and ground is

recommended for proper operation.

PVCC1

This is the positive supply for the lower gate driver, LGATE1.

PVCC1 is connected to a well decoupled 5V.

SENSE1 and SENSE2

Both SENSE1 and SENSE2 are connected directly to the

regulated outputs of the V

respectively. SENSE1 is used as an input to create the

voltage at VREF_OUT and the reference voltage for the V

supply. SENSE2 is used as the regulation point for the

window regulator that is enabled in V2_SD mode.

Functional Description

Overview

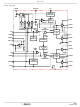

The ISL6530 contains control and drive circuitry for two

synchronous buck PWM voltage regulators. Both regulators

utilize 5V bootstrapped output topology to allow use of low

cost N-channel MOSFETs. The regulators are driven by

DDQ

via a low current window regulator which drives V

TT

supply “floats”, it is held to about 50% of

TT

is controlled to 50% of V

DDQ

7

and V

TT

.

TT

supplies,

DDQ

DDQ

TT

supply has

TT

.

error

supply. A

DDQ

TT

TT

ISL6530

300kHz clocks. The clocks are phase locked and displaced

90

The first regulator includes a precision 0.8V reference and is

intended to provide the proper V

system. The V

protection utilizing the r

Following a fault condition, the V

via a digital softstart circuit.

Included in the ISL6530 is a precision V

output. V

is derived via a precision internal resistor divider connected

to the SENSE1 terminal.

The second PWM regulator is designed to provide V

termination for the DDRAM signal lines. The reference to the

V

termination voltage equal to .5xV

MOSFET of the V

V

sinking and sourcing current on the V

Two benefits result from the ISL6530 dual controller

topology. First, as VREF is always .5xV

will track the V

the overcurrent protection incorporated into the V

will simultaneously protect the V

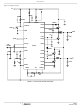

Initialization

The ISL6530 automatically initializes upon application of

input power. Special sequencing of the input supplies is not

necessary. The Power-On Reset (POR) function continually

monitors the input bias supply voltage at the VCC pin. The

POR function initiates soft-start operation after the 5V bias

supply voltage exceeds its POR threshold.

Soft-Start

The POR function initiates the digital soft start sequence. The

PWM error amplifier reference input for the VDDQ regulator is

clamped to a level proportional to the soft-start voltage. As the

soft-start voltage slews up, the PWM comparator generates

PHASE pulses of increasing width that charge the output

capacitor(s). This method provides a rapid and controlled

output voltage rise. The soft start sequence typically takes

about 7ms.

With the V

automatically track the ramp of the V

enabling a soft-start for V

Figure 2 shows the soft-start sequence for a typical application.

At t0, the +5V VCC bias voltage starts to ramp. Once the

voltage on VCC crosses the POR threshold at time t1, both

outputs begin their soft-start sequence. The triangle waveforms

from the PWM oscillators are compared to the rising error

amplifier output voltage. As the error amplifier voltage

increases, the pulse-widths on the UGATE pins increase to

reach their steady-state duty cycle at time t2.

TT

DDQ

o

to minimize noise coupling between the controllers.

regulator is V

voltage. The V

REF

TT

regulator reference held at

is a buffered representation of .5xV

DDQ

DDQ

TT

REF

controller implements overcurrent

supply during softstart cycles. Second,

TT

supply is connected to the regulated

. Thus the V

DS(ON)

controller is designed to enable both

TT

.

of the upper MOSFET.

DDQ

TT

DDQ

DDQ

TT

supply.

DDQ

regulator provides a

. The drain of the upper

to a DDRAM memory

regulator is softstarted

TT

DDQ

REF

rail.

1

-- - V

2

softstart, thus

⋅

, the V

reference

DDQ

November 15, 2004

DDQ

DDQ

TT

it will

TT

. V

supply

supply

FN9052.2

REF