AD9956/PCB Analog Devices Inc, AD9956/PCB Datasheet - Page 24

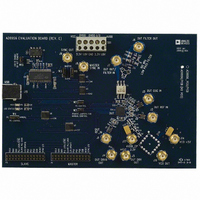

AD9956/PCB

Manufacturer Part Number

AD9956/PCB

Description

BOARD EVAL FOR AD9956

Manufacturer

Analog Devices Inc

Datasheet

1.AD9956YCPZ.pdf

(32 pages)

Specifications of AD9956/PCB

Module/board Type

Evaluation Board

For Use With/related Products

AD9956

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

AD9956

REGISTER MAP AND DESCRIPTION

Table 5.

Register

Name

(Serial

Address)

Control

Function

Register 1

(CFR1)

(0x00)

Control

Function

Register 2

(CFR2)

(0x01)

Rising Delta

Frequency

Tuning

Word

(RDFTW)

(0x02)

Falling Delta

Frequency

Tuning

Word

(FDFTW)

(0x03)

Rising

Sweep

Ramp Rate

(RSRR)

(0x04)

Falling

Sweep

Ramp Rate

(FSRR)

(0x05)

1

In all cases, open bits must be written to 0.

Bit

Range

<31:24>

<23:16>

<15:8>

<7:0>

<39:32>

<31:24>

<23:16>

<15:8>

<7:0>

<23:16>

<15:8>

<7:0>

<23:16>

<15:8>

<7:0>

<15:8>

<7:0>

<15:8>

<7:0>

Open

Open

(MSB) Bit 7

LOAD SRR @

I/O_UPDATE

LSB First

Digital

Power-

Down

DAC

Power-

Down

RF Divider

Power-

Down

Clock Driver Rising Edge <31:29>

1

1

Divider N Control <15:12>

Bit 6

Open

Auto-Clr

Frequency

Accum.

SDI/O

Input

Only

PFD Input

Power-

Down

Open

RF Divider Ratio

<22:21>

Open

1

1

1

Falling Delta Frequency Tuning Word <23:16>

Rising Delta Frequency Tuning Word <23:16>

Falling Delta Frequency Tuning Word <15:8>

Rising Delta Frequency Tuning Word <15:8>

Falling Delta Frequency Tuning Word <7:0>

Bit 5

Open

Auto-

Clr

Phase

Accum.

Open

PLLREF

Crystal

Enable

Open

CP

Polarity

Rising Delta Frequency Tuning Word <7:0>

Rev. A | Page 24 of 32

1

1

1

Rising Sweep Ramp Rate <15:8>

Rising Sweep Ramp Rate <15:8>

Rising Sweep Ramp Rate <7:0>

Rising Sweep Ramp Rate <7:0>

Bit 4

Open

Enable

Sine

Output

Open

SYNC_CLK

Disable

Open

Clock Driver Falling Edge Control

<28:26>

Clock

Driver

Power-

Down

CP

Full PD

1

1

1

Bit 3

Open

Clear

Frequency

Accum.

Open

Auto Sync

Multiple

AD9956s

Open

Clock Driver Input

Select <19:18>

CP

Quick PD

1

1

1

Divider M Control <11:8>

Bit 2

Open

Clear

Phase

Accum.

Open

Software

Manual

Sync

Open

1

1

1

CP Current Scale <2:0>

Bit 1

Open

Linear

Sweep

Enable

Open

Hardware

Manual

Sync

Internal

Band Gap

Power-

Down

PLL Lock

Detect

Enable

Slew Rate

Control

1

1

Bit 0

(LSB)

PLL Lock

Error

Linear

Sweep

No Dwell

Open

High

Speed

Sync

Enable

Internal

CML

Driver

DRV_RSET

PLL Lock

Detect

Mode

RF Div

REFCLK

Mux Bit

1

Default

Value/

Profile

0x00

0x00

0x00

0x00

0x00

0x00

0x78

0x00

0x07

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00