74lvx574 STMicroelectronics, 74lvx574 Datasheet

74lvx574

Available stocks

Related parts for 74lvx574

74lvx574 Summary of contents

Page 1

... PIN AND FUNCTION COMPATIBLE WITH 74 SERIES 574 IMPROVED LATCH-UP IMMUNITY DESCRIPTION The 74LVX574 is a low voltage CMOS OCTAL D-TYPE FLIP-FLOP with 3 STATE OUTPUT NON INVERTING fabricated with sub-micron silicon gate and double-layer metal wiring C technology ideal for low power, battery operated and low noise 3 ...

Page 2

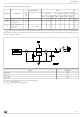

... Figure 2: Input Equivalent Circuit Table 3: Truth Table Don’t Care Z : High Impedance Figure 3: Logic Diagram This logic diagram has not be used to estimate propagation delays 2/13 Table 2: Pin Description PIN N° 12, 13, 14, 15, 16, 17, ...

Page 3

... Value -55 to 125 0 to 100 Value = 25°C -40 to 85°C -55 to 125°C Typ. Max. Min. Max. Min. 1.5 1.5 2.0 2.0 2.4 2.4 0.5 0.5 0.8 0.8 0.8 0.8 2.0 1.9 1.9 3.0 2.9 2.9 2.48 2.4 0.0 0.1 0.1 0.0 0.1 0.1 0.36 0.44 0.25 2.5 0 74LVX574 Unit °C °C Unit °C ns/V Unit Max. V 0.5 0.8 V 0.8 V 0.1 0.1 V 0.55 2 3/13 ...

Page 4

... Table 7: Dynamic Switching Characteristics Symbol Parameter V Dynamic Low OLP Voltage Quiet V OLV Output (note 1, 2) Dynamic High V Voltage Input IHD (note 1, 3) Dynamic Low V Voltage Input ILD (note Worst case package. 2) Max number of outputs defined as (n). Data inputs are driven 0V to 3.3V, (n-1) outputs switching and one output at GND. ...

Page 5

... T OUT Test Condition (V) Min. 3.3 3 10MHz 3.3 IN TEST Value = 25°C -40 to 85°C -55 to 125°C A Typ. Max. Min. Max. Min CC(opr SWITCH Open V GND 74LVX574 Unit Max (per circuit 5/13 ...

Page 6

... Figure 5: Waveform - Propagation Delays Setup And Hold Times (f=1MHz; 50% duty cycle) Figure 6: Waveform - Output Enable And Disable Times (f=1MHz; 50% duty cycle) 6/13 ...

Page 7

... Figure 7: Waveform - CK Minimum Pulse Width (f=1MHz; 50% duty cycle) 74LVX574 7/13 ...

Page 8

... DIM. MIN. A 2.35 A1 0.1 B 0.33 C 0.23 D 12. 10.00 h 0.25 L 0.4 k 0° ddd 8/13 SO-20 MECHANICAL DATA mm. TYP MAX. 2.65 0.30 0.51 0.32 13.00 7.6 1.27 10.65 0.75 1.27 8° 0.100 inch MIN. TYP. 0.093 0.004 0.013 0.009 0.496 0.291 0.050 0.394 0.010 0.016 0° 0016022D MAX. 0.104 0.012 0.020 0.013 0.512 0.299 0.419 0.030 0.050 8° ...

Page 9

... K 0˚ PIN 1 IDENTIFICATION 1 mm. TYP MAX. 1.2 0.15 1 1.05 0.30 0.20 6.5 6.6 6.4 6.6 4.4 4.48 0.65 BSC 8˚ 0.60 0. 74LVX574 inch MIN. TYP. 0.002 0.004 0.031 0.039 0.007 0.004 0.252 0.256 0.244 0.252 0.169 0.173 0.0256 BSC 0˚ 0.018 0.024 0087225C MAX. 0.047 0.006 0.041 0.012 ...

Page 10

... DIM. MIN 12 10.8 Bo 13.2 Ko 3.1 Po 3.9 P 11.9 10/13 Tape & Reel SO-20 MECHANICAL DATA mm. TYP MAX. 330 13.2 30.4 11 13.4 3.3 4.1 12.1 inch MIN. TYP. 12.992 0.504 0.795 2.362 0.425 0.520 0.122 0.153 0.468 MAX. 0.519 1.197 0.433 0.528 0.130 0.161 0.476 ...

Page 11

... Tape & Reel TSSOP20 MECHANICAL DATA DIM. MIN 12 6.8 Bo 6.9 Ko 1.7 Po 3.9 P 11.9 mm. TYP MAX. 330 13.2 0.504 0.795 2.362 22.4 7 0.268 7.1 0.272 1.9 0.067 4.1 0.153 12.1 0.468 74LVX574 inch MIN. TYP. MAX. 12.992 0.519 0.882 0.276 0.280 0.075 0.161 0.476 11/13 ...

Page 12

... Table 10: Revision History Date Revision 27-Aug-2004 3 12/13 Description of Changes Ordering Codes Revision - pag. 1. ...

Page 13

... Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America All other names are the property of their respective owners © 2004 STMicroelectronics - All Rights Reserved STMicroelectronics group of companies www.st.com 74LVX574 13/13 ...