ds2761 Maxim Integrated Products, Inc., ds2761 Datasheet

ds2761

Available stocks

Related parts for ds2761

ds2761 Summary of contents

Page 1

... Low Power Consumption: - Active Current: 60mA typ, 90mA max - Sleep Current: 1mA typ, 2mA max * Mechanical drawing for the 16-pin TSSOP and DS2761 flip-chip package can be found at: http://pdfserv.maxim-ic.com/arpdf/Packages/16tssop.pdf http://pdfserv.maxim-ic.com/arpdf/Packages/chips/2761x.pdf 1-Wire is a registered trademark of Dallas Semiconductor. High-Precision Li+ Battery Monitor ...

Page 2

... This low-power device integrates precise temperature, voltage, and current measurement, nonvolatile (NV) data storage, and Li+ protection into the small footprint of either a TSSOP package or flip-chip package. The DS2761 is a key component in applications including remaining capacity estimation, safety monitoring, and battery-specific data storage ...

Page 3

... Three types of memory are provided on the DS2761 for battery information storage: EEPROM, lockable EEPROM, and SRAM. EEPROM memory saves important battery data in true NV memory that is unaffected by severe battery depletion, accidental shorts, or ESD events. Lockable EEPROM becomes ROM when locked to provide additional security for unchanging battery data. SRAM provides inexpensive storage for temporary data ...

Page 4

... Programmable I/O Pin. Used to control and monitor user-defined external circuitry. Open drain to VSS. Battery Pack Positive Terminal Input. The DS2761 monitors the pack plus terminal through PLS to detect overcurrent and overload conditions, as well as the presence of a charge source. Additionally, a charge path to recover a deeply depleted cell is provided from PLS to V ...

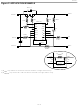

Page 5

... DS2761 PLS V DD 150 W DC PIO SNS V SS SNS V SS 150 W SNS IS2 IS1 104 150 104 4.7k W (1) R SNS (2) R SNS-INT SNS R KS IS2 voltage sense DS2761 BAT+ PS BAT IS1 ...

Page 6

... With test current I flowing from V TST Overvoltage. If the cell voltage on V overvoltage delay the DS2761 shuts off the external charge FET and sets the OV flag in the OVD protection register. When the cell voltage falls below charge enable threshold V ACTIVATION THRESHOLD DELAY V > ...

Page 7

... IS Undervoltage. If the voltage of the cell drops below undervoltage threshold V undervoltage delay t , the DS2761 shuts off the charge and discharge FETs, sets the UV flag in the UVD protection register, and enters sleep mode. The DS2761 provides a current-limited recovery charge path from PLS gently charge severely depleted cells during sleep mode ...

Page 8

... (Sleep Mode) CURRENT MEASUREMENT In the active mode of operation, the DS2761 continually measures the current flow into and out of the battery by measuring the voltage drop across a current-sense resistor. The DS2761 is available in two configurations: 1) internal 25mW current-sense resistor, and 2) external user-selectable sense resistor. In ...

Page 9

... When the internal sense resistor is used, the DS2761 maintains the current accumulator in units of amp- hours, with a resolution of 0.25mAhrs and full-scale range of ±8.2Ahrs. When using an external sense resistor, the DS2761 maintains the current accumulator in units of volt-hours, with a resolution of 6.25mVhrs and a full scale range of ±205mVhrs. ...

Page 10

... PIO bit disables the output driver, allowing the PIO pin to be pulled high or used as an input. To sense the value on the PIO pin, read the PIO bit. The DS2761 turns off the PIO output driver and sets the PIO bit high when in sleep mode or when DQ is low for more than 2s, regardless of the state of the PMOD bit ...

Page 11

... MEMORY The DS2761 has a 256-byte linear address space with registers for instrumentation, status, and control in the lower 32 bytes, with lockable EEPROM and SRAM memory occupying portions of the remaining address space. All EEPROM and SRAM memory is general purpose except addresses 30h, 31h, and 33h, which should be written with the default values for the protection register, status register, and current offset register, respectively ...

Page 12

... DE—Discharge Enable. Writing this bit disables discharging ( DC output high, external discharge FET off) regardless of cell or pack conditions. Writing this bit enables discharging, subject to override by the presence of any protection conditions. The DS2761 automatically sets this bit to 1 when it transitions from sleep mode to active mode. ...

Page 13

... X X PMOD—Sleep Mode Enable. A value this bit enables the DS2761 to enter sleep mode when the DQ line goes low for greater than 2s and to leave sleep mode when the DQ line goes high. A value of 0 disables DQ-related transitions into and out of sleep mode. This bit is read-only. The desired default value should be set in bit 5 of address 31h. The factory default is 0. RNAOP— ...

Page 14

... Each DS2761 has a unique, factory-programmed 1-Wire net address that is 64 bits in length. The first eight bits are the 1-Wire family code (30h for DS2761). The next 48 bits are a unique serial number. The last eight bits are a cyclic redundancy check (CRC) of the first 56 bits (see Figure 13). The 64-bit net address and the 1-Wire I/O circuitry built into the device enable the DS2761 to communicate through the 1-Wire protocol detailed in the 1-Wire Bus System section of this data sheet ...

Page 15

... To facilitate this, each device attached to the 1-Wire bus must connect to the bus with open-drain or tri-state output drivers. The DS2761 used an open-drain output driver as part of the bidirectional interface circuitry shown in Figure 15 bidirectional pin is not available on the bus master, separate output and input pins can be connected together ...

Page 16

... This command can be used with one or more slave devices on the bus. Skip Net Address [CCh]. This command saves time when there is only one DS2761 on the bus by allowing the bus master to issue a function command without specifying the address of the slave. If more than one slave device is present on the bus, a subsequent function command can cause a data collision when all slaves transmit data at the same time ...

Page 17

... The term power control refers to the ability of the DS2761 to control the flow of power into or out the battery pack using control pins DC and CC . The SWAP command is issued followed by the net address. ...

Page 18

Table 4. FUNCTION COMMANDS COMMAND DESCRIPTION Reads data from Read Data memory starting at address XX Writes data to memory Write Data starting at address XX Copies shadow RAM Copy Data data to EEPROM block containing address XX Recalls EEPROM ...

Page 19

... NET ADDRESS COMMAND NO F0h NO SEARCH YES DS2761 Tx BIT 0 DS2761 Tx BIT 0 MASTER Tx BIT BIT 0 MATCH ? YES DS2761 Tx BIT 1 DS2761 Tx BIT 1 MASTER Tx BIT BIT 1 MATCH ? YES YES DS2761 Tx BIT 63 DS2761 Tx BIT 63 MASTER Tx BIT 63 FALLING EDGE OF DQ DS2761 TO SLEEP MODE AAh ...

Page 20

... The bus master must keep the bus line low for at least 1 DS2761 to present valid data. The bus master can then sample the data t read-time slot. By the end of the read-time slot, the DS2761 releases the bus line and allows pulled high by the external pullup resistor. All read-time slots must be t ...

Page 21

... BOTH BUS MASTER AND DS2761 ACTIVE LOW t SWL t SWOFF WRITE 1 SLOT t SLOT t LOW1 DS2761 SAMPLE WINDOW MIN TYP MAX 15ms 15ms 30ms READ 1 SLOT t SLOT t REC MASTER SAMPLE WINDOW t RDV DS2761 ACTIVE LOW RESISTOR PULLUP t SWON PACK+ PACK- PACK+ PACK– ...

Page 22

ABSOLUTE MAXIMUM RATINGS* Voltage on PLS and CC Pin, Relative to V Voltage on PIO Pin, Relative to V Voltage on VIN and PS , Relative to V Voltage on any Other Pin, Relative to V Continuous Internal Sense Resistor ...

Page 23

ELECTRICAL CHARACTERISTICS: PROTECTION CIRCUITRY PARAMETER Overvoltage Detect Charge Enable Undervoltage Detect Overcurrent Detect Overcurrent Detect Short-Circuit Detect Short-Circuit Detect Overvoltage Delay Undervoltage Delay Overcurrent Delay Short-Circuit Delay Test Threshold Test Current Recovery Charge Current ELECTRICAL CHARACTERISTICS: TEMPERATURE, VOLTAGE, CURRENT PARAMETER ...

Page 24

... DS2761 compensates for the internal sense resistor’s temperature coefficient of 3700ppm/° accuracy of ±500ppm/°C. The DS2761 does not compensate for external sense resistor characteristics, and any error terms arising from the use of an external sense resistor should be taken into account when calculating total current measurement error ...