IDT71V67903 Integrated Device Technology, IDT71V67903 Datasheet

IDT71V67903

Available stocks

Related parts for IDT71V67903

IDT71V67903 Summary of contents

Page 1

... Core Power, I/O Power DD DDQ V Ground SS NOTE and BW are not applicable for the IDT71V67903 ©2002 Integrated Device Technology, Inc. 256K X 36, 512K X 18 3.3V Synchronous SRAMs 3.3V I/O, Burst Counter Flow-Through Outputs, Single Cycle Deselect data, address and control registers. There are no registers in the data output path (flow-through architecture) ...

Page 2

... IDT71V67703, IDT71V67903, 256K x 36, 512K x 18, 3.3V Synchronous SRAMS with 3.3V I/O, Flow-Through Outputs, Single Cycle Deselect Symbol Pin Function I Address Inputs Address Status I (Cache Controller) Address Status I (Processor) Burst Address I Advance Byte Write Enable I Individual Byte Write Enables Chip Enable ...

Page 3

... IDT71V67703, IDT71V67903, 256K x 36, 512K x 18, 3.3V Synchronous SRAMS with 3.3V I/O, Flow-Through Outputs, Single Cycle Deselect LBO AD V CLK AD SC ADSP A A 0– 17/ Powerdown O E 36/18 I/O –I I/O I/O P1– P4 Commercial and Industrial Temperature Ranges Burst ...

Page 4

... IDT71V67703, IDT71V67903, 256K x 36, 512K x 18, 3.3V Synchronous SRAMS with 3.3V I/O, Flow-Through Outputs, Single Cycle Deselect Symbol Rating (2) V Terminal Voltage with TERM Respect to GND (3,6) V Terminal Voltage with TERM Respect to GND (4,6) V Terminal Voltage with TERM Respect to GND (5,6) V Terminal Voltage with TERM Respect to GND ...

Page 5

... IDT71V67703, IDT71V67903, 256K x 36, 512K x 18, 3.3V Synchronous SRAMS with 3.3V I/O, Flow-Through Outputs, Single Cycle Deselect DDQ I DDQ DDQ V 21 ...

Page 6

... IDT71V67703, IDT71V67903, 256K x 36, 512K x 18, 3.3V Synchronous SRAMS with 3.3V I/O, Flow-Through Outputs, Single Cycle Deselect 100 DDQ I I DDQ ...

Page 7

... IDT71V67703, IDT71V67903, 256K x 36, 512K x 18, 3.3V Synchronous SRAMS with 3.3V I/O, Flow-Through Outputs, Single Cycle Deselect DDQ I I DDQ DDQ DDQ DDQ DDQ I ...

Page 8

... IDT71V67703, IDT71V67903, 256K x 36, 512K x 18, 3.3V Synchronous SRAMS with 3.3V I/O, Flow-Through Outputs, Single Cycle Deselect I/O I I/O I I/O I I I/O I I/O I I/O I I/O I I/O NC ...

Page 9

... IDT71V67703, IDT71V67903, 256K x 36, 512K x 18, 3.3V Synchronous SRAMS with 3.3V I/O, Flow-Through Outputs, Single Cycle Deselect Symbol Parameter |I | Input Leakage Current LI ( Input Leakage Current Output Leakage Current LO V Output Low Voltage OL V Output High Voltage OH NOTE: 1. The LBO pin will be internally pulled to V ...

Page 10

... IDT71V67703, IDT71V67903, 256K x 36, 512K x 18, 3.3V Synchronous SRAMS with 3.3V I/O, Flow-Through Outputs, Single Cycle Deselect Operation Address Used Deselected Cycle, Power Down None Deselected Cycle, Power Down None Deselected Cycle, Power Down None Deselected Cycle, Power Down None Deselected Cycle, Power Down ...

Page 11

... IDT71V67703, IDT71V67903, 256K x 36, 512K x 18, 3.3V Synchronous SRAMS with 3.3V I/O, Flow-Through Outputs, Single Cycle Deselect Operation Read Read Write all Bytes Write all Bytes (3) Write Byte 1 (3) Write Byte 2 (3) Write Byte 3 (3) Write Byte 4 NOTES Don’t Care. ...

Page 12

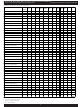

... IDT71V67703, IDT71V67903, 256K x 36, 512K x 18, 3.3V Synchronous SRAMS with 3.3V I/O, Flow-Through Outputs, Single Cycle Deselect Symbol Clock Parameter t Clock Cycle Time CYC (1) Clock High Pulse Width t CH (1) Clock Low Pulse Width t CL Output Parameters t Clock High to Valid Data CD t Clock High to Data Change ...

Page 13

... IDT71V67703, IDT71V67903, 256K x 36, 512K x 18, 3.3V Synchronous SRAMS with 3.3V I/O, Flow-Through Outputs, Single Cycle Deselect Commercial and Industrial Temperature Ranges , 6.42 13 ...

Page 14

... IDT71V67703, IDT71V67903, 256K x 36, 512K x 18, 3.3V Synchronous SRAMS with 3.3V I/O, Flow-Through Outputs, Single Cycle Deselect Commercial and Industrial Temperature Ranges 6. ...

Page 15

... IDT71V67703, IDT71V67903, 256K x 36, 512K x 18, 3.3V Synchronous SRAMS with 3.3V I/O, Flow-Through Outputs, Single Cycle Deselect Commercial and Industrial Temperature Ranges GW 6. ...

Page 16

... IDT71V67703, IDT71V67903, 256K x 36, 512K x 18, 3.3V Synchronous SRAMS with 3.3V I/O, Flow-Through Outputs, Single Cycle Deselect Commercial and Industrial Temperature Ranges 6. ...

Page 17

... IDT71V67703, IDT71V67903, 256K x 36, 512K x 18, 3.3V Synchronous SRAMS with 3.3V I/O, Flow-Through Outputs, Single Cycle Deselect Commercial and Industrial Temperature Ranges , 6.42 17 ...

Page 18

... IDT71V67703, IDT71V67903, 256K x 36, 512K x 18, 3.3V Synchronous SRAMS with 3.3V I/O, Flow-Through Outputs, Single Cycle Deselect CLK ADDRESS CE DATA OUT NOTES input is LOW, ADV is HIGH and LBO is Don't Care for this cycle. 2. (Ax) represents the data for address Ax, etc. ...

Page 19

... IDT71V67703, IDT71V67903, 256K x 36, 512K x 18, 3.3V Synchronous SRAMS with 3.3V I/O, Flow-Through Outputs, Single Cycle Deselect Commercial and Industrial Temperature Ranges 6.42 19 ...

Page 20

... IDT71V67703, IDT71V67903, 256K x 36, 512K x 18, 3.3V Synchronous SRAMS with 3.3V I/O, Flow-Through Outputs, Single Cycle Deselect Commercial and Industrial Temperature Ranges 6.42 20 ...

Page 21

... IDT71V67703, IDT71V67903, 256K x 36, 512K x 18, 3.3V Synchronous SRAMS with 3.3V I/O, Flow-Through Outputs, Single Cycle Deselect Commercial and Industrial Temperature Ranges 6.42 21 ...

Page 22

... IDT71V67703, IDT71V67903, 256K x 36, 512K x 18, 3.3V Synchronous SRAMS with 3.3V I/O, Flow-Through Outputs, Single Cycle Deselect IDT XXX S X Device Power Speed Package Type XX X Process/ Temperature Rance Commercial (0°C to +70° C) Blank Industrial (-40° +85° 100-Pin Plastic Thin Quad Flatpack (TQFP) ...

Page 23

... IDT71V67703, IDT71V67903, 256K x 36, 512K x 18, 3.3V Synchronous SRAMS with 3.3V I/O, Flow-Through Outputs, Single Cycle Deselect 12/31/99 Created Datasheet from 71V677 and 71V679 Datasheets For 2.5V I/O offering, see 71V67702 AND 71V67902 Datasheets. 04/26/00 Pg. 4 Add capacitance for BGA package; Insert clarification note to Absolute Max Ratings and Recommended Operating Temperature tables. Replace Pin U6 with TRST pin in BGA pin configuration ...