IDT82V1054APF IDT, Integrated Device Technology Inc, IDT82V1054APF Datasheet

IDT82V1054APF

Specifications of IDT82V1054APF

Available stocks

Related parts for IDT82V1054APF

IDT82V1054APF Summary of contents

Page 1

QUAD PROGRAMMABLE PCM CODEC WITH MPI INTERFACE FEATURES • 4-channel CODEC with on-chip digital filters • Software selectable A/ -law, linear code conversion µ • Meets ITU-T G.711 - G.714 requirements • Programmable digital filters adapting to system demands: - ...

Page 2

IDT82V1054A QUAD PROGRAMMABLE PCM CODEC WITH MPI INTERFACE DESCRIPTION The IDT82V1054A is a feature rich, single-chip, programmable 4- channel PCM CODEC with on-chip filters. Besides the companding and linear coding/decoding (14 effective bits + 2 extra sign bits), the IDT82V1054A ...

Page 3

IDT82V1054A QUAD PROGRAMMABLE PCM CODEC WITH MPI INTERFACE 1 Pin Description...................................................................................................................................................................................................7 2 Functional Description ......................................................................................................................................................................................9 2.1 MPI/PCM Interface ....................................................................................................................................................................................9 2.1.1 Microprocessor Interface (MPI) ....................................................................................................................................................9 2.1.2 PCM Bus ....................................................................................................................................................................................10 2.2 DSP Programming...................................................................................................................................................................................11 2.2.1 Signal Processing.......................................................................................................................................................................11 2.2.2 Gain Adjustment.........................................................................................................................................................................11 2.2.3 Impedance Matching ...

Page 4

IDT82V1054A QUAD PROGRAMMABLE PCM CODEC WITH MPI INTERFACE 7.7 Interchannel Crosstalk.............................................................................................................................................................................36 7.8 Intrachannel Crosstalk.............................................................................................................................................................................36 8 Timing Characteristics ....................................................................................................................................................................................37 8.1 Clock Timing............................................................................................................................................................................................37 8.2 Microprocessor Interface Timing .............................................................................................................................................................38 8.3 PCM Interface Timing..............................................................................................................................................................................39 9 Appendix: IDT82V1054A Coe-RAM Mapping.................................................................................................................................................40 10 Ordering Information .......................................................................................................................................................................................41 INDUSTRIAL ...

Page 5

IDT82V1054A QUAD PROGRAMMABLE PCM CODEC WITH MPI INTERFACE Figure - 1 An Example of the MPI Interface Write Operation .............................................................................................................................. 9 Figure - 2 An Example of the MPI Interface Read Operation (ID = 81H)............................................................................................................. 9 Figure - 3 Sampling ...

Page 6

IDT82V1054A QUAD PROGRAMMABLE PCM CODEC WITH MPI INTERFACE Table - 1 Consecutive Adjacent Addressing......................................................................................................................................................15 Table - 2 Global Registers (GREG) Mapping ....................................................................................................................................................20 Table - 3 Local Registers (LREG) Mapping.......................................................................................................................................................21 Table - 4 Coe-RAM Address Allocation.............................................................................................................................................................40 LIST OF TABLES 6 INDUSTRIAL ...

Page 7

IDT82V1054A QUAD PROGRAMMABLE PCM CODEC WITH MPI INTERFACE 1 PIN DESCRIPTION Name Type Pin Number GNDA1 50 GNDA2 54 Ground GNDA3 59 GNDA4 63 GNDD Ground 21 VDDA12 52 Power VDDA34 61 VDDD Power 24 VDDB Power 57 − CNF ...

Page 8

IDT82V1054A QUAD PROGRAMMABLE PCM CODEC WITH MPI INTERFACE Name Type Pin Number 25 TSX1 0 TSX2 CCLK I 18 MCLK I 22 RESET I 23 INT12 O 34 INT34 O ...

Page 9

IDT82V1054A QUAD PROGRAMMABLE PCM CODEC WITH MPI INTERFACE 2 FUNCTIONAL DESCRIPTION The IDT82V1054A is a four-channel PCM CODEC with on-chip digital filters. It provides a four-wire solution for the subscriber line circuitry in digital switches. The IDT82V1054A converts analog voice ...

Page 10

IDT82V1054A QUAD PROGRAMMABLE PCM CODEC WITH MPI INTERFACE 2.1.2 PCM BUS The IDT82V1054A provides two flexible PCM buses for all 4 channels. The digital PCM data can be compressed (A/ code. As shown in Figure - 3, the data rate ...

Page 11

IDT82V1054A QUAD PROGRAMMABLE PCM CODEC WITH MPI INTERFACE 2.2 DSP PROGRAMMING 2.2.1 SIGNAL PROCESSING Several blocks are programmable for signal processing. This allows users to optimize the performance of the IDT82V1054A for the system. Figure - 4 shows the signal ...

Page 12

IDT82V1054A QUAD PROGRAMMABLE PCM CODEC WITH MPI INTERFACE (IMF) and Gain of Impedance Scaling filter (GIS) work together to realize impedance matching. If the CS[0] bit in LREG1 is ‘0’, the IMF is disabled. If the CS[0] bit is ‘1’, ...

Page 13

IDT82V1054A QUAD PROGRAMMABLE PCM CODEC WITH MPI INTERFACE specified channel. When one bit of IE[4:0] is ‘0’, the corresponding interrupt is ignored (disabled), otherwise, the corresponding interrupt is recognized (enabled). Multiple interrupt sources can be enabled at the same time. ...

Page 14

IDT82V1054A QUAD PROGRAMMABLE PCM CODEC WITH MPI INTERFACE corresponds to the minimum amplitude linear relationship between 'A' and the amplitude. That is, if A=β ( 0<β<1), the amplitude will be 1.57 ...

Page 15

IDT82V1054A QUAD PROGRAMMABLE PCM CODEC WITH MPI INTERFACE 3 OPERATING THE IDT82V1054A 3.1 PROGRAMMING DESCRIPTION The IDT82V1054A is programmed by writing commands to registers and coefficient RAM. A Channel Program Enable register (GREG6) is provided for addressing individual or multiple ...

Page 16

IDT82V1054A QUAD PROGRAMMABLE PCM CODEC WITH MPI INTERFACE tone coefficients, can only be addressed on a per-channel basis. Therefore, users should specify a channel (by setting the corresponding CE bit in GREG6 to ‘1’) before writing/reading tone coefficients to/from the ...

Page 17

IDT82V1054A QUAD PROGRAMMABLE PCM CODEC WITH MPI INTERFACE data byte 14 low byte of word 2 of block 1 data byte 15 high byte of word 1 of block 1 data byte 16 low byte of word 1 of block ...

Page 18

IDT82V1054A QUAD PROGRAMMABLE PCM CODEC WITH MPI INTERFACE data byte 4 data read out from low byte of word 7 of block 3 data byte 5 data read out from high byte of word 6 of block 3 data byte ...

Page 19

IDT82V1054A QUAD PROGRAMMABLE PCM CODEC WITH MPI INTERFACE 3.2 POWER-ON SEQUENCE To power on the IDT82V1054A, users should follow the sequence below: 1. Apply ground first; 2. Apply VCC, finish signal connections and set the RESET pin to logic low. ...

Page 20

IDT82V1054A QUAD PROGRAMMABLE PCM CODEC WITH MPI INTERFACE 3.4 REGISTERS DESCRIPTION 3.4.1 REGISTERS OVERVIEW Table - 2 Global Registers (GREG) Mapping Name Function b7 Version number (read)/ GREG1 no operation (write) GREG2 Interrupt clear GREG3 Software reset GREG4 Hardware reset ...

Page 21

IDT82V1054A QUAD PROGRAMMABLE PCM CODEC WITH MPI INTERFACE Table - 3 Local Registers (LREG) Mapping Name Function b7 LREG1 Coefficient selection CS[7] Local loopbacks LREG2 control and SLIC input IE[4] interrupt enable DSH and GK LREG3 debounce filters GK[3] configuration ...

Page 22

IDT82V1054A QUAD PROGRAMMABLE PCM CODEC WITH MPI INTERFACE For the global and local registers described below, it should be noted that Read command. R Write command. 2. The reserved bit(s) in the registers must ...

Page 23

IDT82V1054A QUAD PROGRAMMABLE PCM CODEC WITH MPI INTERFACE CHclk1[3:0] = 1001: chclk1 outputs a digital signal with the frequency of 1000/18 Hz; CHclk1[3:0] = 1010: chclk1 outputs a digital signal with the frequency of 1000/20 Hz; CHclk1[3:0] = 1011: chclk1 ...

Page 24

IDT82V1054A QUAD PROGRAMMABLE PCM CODEC WITH MPI INTERFACE The PCM data Offset Configuration bits (OC[2:0]) determine that the transmit and receive time slots of PCM data offset from the FS signal by how many periods of BCLK: OC[2:0] = 000: ...

Page 25

IDT82V1054A QUAD PROGRAMMABLE PCM CODEC WITH MPI INTERFACE GREG10: SB1 Direction Control and SB1 Status/Control Data, Read/Write (29H/A9H) b7 Command R/W I/O data SB1C[3] The SB1 direction control bits SB1C[3:0] in this register determine the directions of the SB1 pins ...

Page 26

IDT82V1054A QUAD PROGRAMMABLE PCM CODEC WITH MPI INTERFACE pins respectively. When the SB3 pins of Channel 1 to Channel 4 are configured as outputs, the control data is written to these four SB3 pins via the SB3[0] to SB3[3] bits ...

Page 27

IDT82V1054A QUAD PROGRAMMABLE PCM CODEC WITH MPI INTERFACE The Level Meter Channel Select bits (CS[1:0]) select a channel, data on which will be level metered. CS[1:0] = 00: Channel 1 is selected (default); CS[1:0] = 01: Channel 2 is selected; ...

Page 28

IDT82V1054A QUAD PROGRAMMABLE PCM CODEC WITH MPI INTERFACE 3.4.3 LOCAL REGISTERS LIST LREG1: Coefficient Selection, Read/Write (00H/80H) b7 Command R/W I/O data CS[7] The Coefficient Select bits (CS[7:0]) are used to control digital filters and function blocks on each channel. ...

Page 29

IDT82V1054A QUAD PROGRAMMABLE PCM CODEC WITH MPI INTERFACE The Loopback Control Bits (DLB_PCM, ALB_1BIT and DLB_1BIT) determine the loopback status on the corresponding channel. Refer to Figure - 4 on page 11 for details. DLB_PCM = 0: Digital Loopback via ...

Page 30

IDT82V1054A QUAD PROGRAMMABLE PCM CODEC WITH MPI INTERFACE LREG4: Channel I/O Data, Read/Write (03H/83H) b7 Command R/W I/O data Reserved The Channel I/O Data bits contain the information of the SLIC I/O pins (SI1, SI2, SB1, SB2, SB3, SO1 and ...

Page 31

IDT82V1054A QUAD PROGRAMMABLE PCM CODEC WITH MPI INTERFACE This register is used for MCU to monitor the transmit ( PCM data. For linear code, this register contains the high byte of the transmit PCM data. For compressed code ...

Page 32

IDT82V1054A QUAD PROGRAMMABLE PCM CODEC WITH MPI INTERFACE 4 ABSOLUTE MAXIMUM RATINGS Power supply voltage Voltage on digital input pins with respect to the ground (including SB1-3 if SB1-3 are configured as inputs) Voltage on analog input pins with respect ...

Page 33

IDT82V1054A QUAD PROGRAMMABLE PCM CODEC WITH MPI INTERFACE 6.3 ANALOG INTERFACE Parameter Description V Output voltage, VOUT OUT1 V Output voltage swing, VOUT OUT2 R Input resistance, VIN I R Output resistance, VOUT O R Load resistance, VOUT L C ...

Page 34

IDT82V1054A QUAD PROGRAMMABLE PCM CODEC WITH MPI INTERFACE 7 TRANSMISSION CHARACTERISTICS 0 dBm0 is defined as 0.5026 Vrms for A-law and 0.49885 Vrms for dBm0, 1020 Hz sine wave; the input amplifier is set for unity gain. The digital input ...

Page 35

IDT82V1054A QUAD PROGRAMMABLE PCM CODEC WITH MPI INTERFACE 7.4 GROUP DELAY Parameter Description Transmit delay, relative to 1800 500 to 600 600 to 1000 1000 to 2600 Hz f ...

Page 36

IDT82V1054A QUAD PROGRAMMABLE PCM CODEC WITH MPI INTERFACE 7.6 NOISE Parameter Description N Transmit noise, C-message weighted for µ-law XC N Transmit noise, psophometrically weighted for A-law XP N Receive noise, C-message weighted for µ-law RC N Receive noise, psophometrically ...

Page 37

IDT82V1054A QUAD PROGRAMMABLE PCM CODEC WITH MPI INTERFACE 8 TIMING CHARACTERISTICS 8.1 CLOCK TIMING Symbol Description t1 CCLK period t2 CCLK pulse width t3 CCLK rise and fall time t4 BCLK period t5 BCLK pulse width t6 BCLK rise and ...

Page 38

IDT82V1054A QUAD PROGRAMMABLE PCM CODEC WITH MPI INTERFACE 8.2 MICROPROCESSOR INTERFACE TIMING Symbol Description t11 CS setup time t12 CS pulse width t13 CS off time t14 Input data setup time t15 Input data hold time t16 SLIC output latch ...

Page 39

IDT82V1054A QUAD PROGRAMMABLE PCM CODEC WITH MPI INTERFACE 8.3 PCM INTERFACE TIMING Symbol Description t21 Data enable delay time t22 Data delay time from BCLK t23 Data float delay time t24 Frame sync setup time t25 Frame sync hold time ...

Page 40

IDT82V1054A QUAD PROGRAMMABLE PCM CODEC WITH MPI INTERFACE 9 APPENDIX: IDT82V1054A COE-RAM MAPPING Block # Word # Generally, 6 bits of address are needed to ...

Page 41

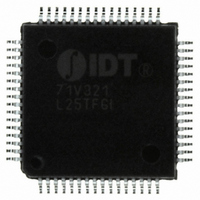

IDT82V1054A QUAD PROGRAMMABLE PCM CODEC WITH MPI INTERFACE 10 ORDERING INFORMATION XXXXXXXX IDT Dev ice Process/ Package Temperature Range Blank PF 82V1054A 41 INDUSTRIAL TEMPERATURE Industrial (-40 °C to +85 °C) Thin Quad Flat Pack ...

Page 42

IDT82V1054A QUAD PROGRAMMABLE PCM CODEC WITH MPI INTERFACE DATA SHEET DOCUMENT HISTORY 01/10/2003 pgs 10, 19, 28, 33, 35, 36, 41 07/28/2003 pgs. 13, 24, 30, 32, 34 12/08/2003 pgs. 1, 11, 34 07/19/2004 pg. 32 CORPORATE HEADQUARTERS ...