LTC1923 LINER [Linear Technology], LTC1923 Datasheet

LTC1923

Available stocks

Related parts for LTC1923

LTC1923 Summary of contents

Page 1

... Typical temperature setpoint accu- racy of 0 achievable with the LTC1923. Adding an instrumentation amplifier front end allows setpoint stabil- ity of 0.01 C. The part features independent adjustable heating and ...

Page 2

... C = 330pF unless otherwise noted CONDITIONS Low to High Threshold High to Low No Output Load, Outputs Not Switching SDSYNC = 0V Measured at PDRVA, PDRVB ORDER PART TOP VIEW NUMBER LTC1923EGN REF 4 PDRVB 25 5 NDRVB PGND SS 8 ...

Page 3

... CS = 100mV – LOAD + – 100mV LOAD (Note 3) + – Measured 0.75V + – 0.5V, Measured – 0.5V, Measured LIM LTC1923 = MIN TYP MAX UNITS 2.462 2.5 2.538 V 2.450 2.550 V 2.25 2. 190 ...

Page 4

... Note 1: Absolute Maximum Ratings are those values beyond which the life of a device may be impaired. Note 2: The LTC1923E is guaranteed to meet specifications from Specifications over the – operating temperature range are assured by design, characterization and correlation with statistical process controls ...

Page 5

... Open Thermistor Threshold vs Temperature 4. SET 4.59 4.58 4.57 4.56 4.55 130 –50 – TEMPERATURE ( C) LTC1923 V vs Temperature REF 2.510 2.505 2.500 2.495 2.490 2.485 20 – –20 TEMPERATURE ( C) 1923 G02 Output Rise/Fall Time vs R 250 200 150 100 ...

Page 6

... LTC1923 W U TYPICAL PERFOR A CE CHARACTERISTICS Current Limit Threshold vs Temperature 165 160 155 150 145 140 135 130 125 – 130 –20 10 100 TEMPERATURE ( C) 1923 G10 6 System Power Loss vs TEC Current 0 0.6 0 3.3V DD 0.2 0 0.5 1 TEC CURRENT (A) 1923 G11 ...

Page 7

... C Baseline Tilt Over Plot Length Derives From Varying Ambient Temperature Identical Test Conditions as Above, Except in Heating Mode. TEC’s Higher Heating Mode Efficiency Results in Higher Thermal Gain. 0.002 C Peak-to-Peak Variation Is 4x Stability Improvement. Baseline Tilt, Just Detectable, Shows Similar 4x Improvement vs Above LTC1923 1923 G13.tif 1923 G14.tif 1923f ...

Page 8

... LTC1923 CTIO S (GN Package/UH Package) PLLLPF (Pin 1/Pin 30): This pin serves as the lowpass filter for the phase-locked loop when the part is being synchronized. The average voltage on this pin equally alters both the oscillator charge and discharge currents, thereby changing the frequency of operation. Bringing the voltage on this pin above V – ...

Page 9

... This pin also sets the dead time between turning one set of outputs off and turning the other set on to ensure the outputs do not cross conduct. The voltage on this pin is regulated to 0.5V. For best performance, the current sourced from the R 150 A. Selecting R provides 90ns of dead time. LTC1923 • ...

Page 10

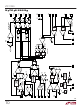

... LTC1923 CTIO AL DIAGRA 10 W 1923f ...

Page 11

... PMOS, MPA, and lower right NMOS, MNA. The gates of these devices are attached to the PDRVA and NDRVA outputs of the LTC1923, respec- tively. The “B” side of the bridge is comprised of PMOS, MPB and NMOS, MNB. The gates of these MOSFETs are controlled by the PDRVB and NDRVB outputs of the LTC1923 ...

Page 12

... U OPERATIO PROTECTION FEATURES Many protection features have been integrated into the LTC1923 to ensure that the TEC is not overstressed or the system does not thermally run away. These features include pulse-by-pulse current limiting, TEC voltage clamp- ing and open/shorted thermistor detection. Current Limit ...

Page 13

... TEC and possibly the components whose temperature is being regulated will occur. 1923 F04 The LTC1923 contains two dedicated comparators that directly monitor the voltage on the thermistor. If this voltage is outside the valid window, a latch is set and the FAULT pin is asserted low. The output drivers are not shut off and the control circuitry is not disabled, meaning the part will continue to try to regulate temperature ...

Page 14

... LTC1923 U OPERATIO pulled to V forcing the gate of M2 low, which allows the DD bridge to operate as described earlier. When a fault occurs and FAULT is asserted low shut off, forcing the gate of M2 high, shutting that device off. The power path is thus opened, ensuring no current is delivered to the TEC. M2 ...

Page 15

... OSC(kHz) and 10k or TE2 The LTC1923 can run at frequencies up to 1MHz. The value selected for R side of the full bridge turning off and the opposite side turning on. This time is also known as the “break-before- make” time. The typical value of 10k will produce a 90ns “ ...

Page 16

... Master/Slave Operation—Set Oscillator Frequency of Slave at 70% to 80% of Master Figure 9. Oscillator Frequency Setup: a) Free Running b) Slaved Operation c) Master/Slave Operation 16 the oscillator is slaved to an external clock. Figure 9c illustrates how one LTC1923 can be used as a master to synchronize other LTC1923s or additional devices requir- ing synchronization. To implement this, determine the values of R ...

Page 17

... TEC manufacturers typically state that N should be no greater than 10%. V BRIDGE I I PDRVA MPA L TEC + L NDRVB MNB ESR TEC C 1/2 V Figure 10. Full-Bridge Half Circuit LTC1923 + I TEC = 5V 2 BRIDGE TEC = 250kHz. The peak-to-peak OSC 2 = 1/( the maximum possible temperature differen TEC BRIDGE 1923 F10 /2 and ...

Page 18

... K THRM K and K IA instrumentation and LTC1923 error amplifier. Switching regulators are sampled systems that convert voltage to duty cycle (d), which explains why the K gain terms are expressed as a function of duty cycle and voltage. The TEC converts voltage to temperature change, while the thermistor’s impedance and therefore voltage across it changes with temperature ...

Page 19

... TEC(MAX MOD LTC1923 + ERROR – R AMP A – Figure 11. Simplified Loop Block Diagram LTC1923 • • • V PWR the C voltage which has a fixed 1V amplitude. T TEC(MAX) = 10k NTC with 4.4 C/1. C PWR TEC V TECOOLER ...

Page 20

... First note that the LTC2053 inputs and F have been swapped as the LTC1923 error amplifier is now running in an inverting configuration. Capacitor C needed to provide the lead term. Resistor R buffer the LTC2053 from capacitive loading and limit the error amplifier high frequency gain ...

Page 21

... The LTC2053 has maximum offset drift to 50nV/ C which translates into less than 0.001 C change for ambient. The offset drift of the LTC1923 error amplifier divided by the gain of the LTC2053 also affects temperature stability. The offset drift of the LTC1923 (see characteristic curves) is typically 1mV over ambient ...

Page 22

... MOSFETs receive nonoverlapping drive. Power MOSFET Selection Four external MOSFETs must be selected for use with the LTC1923; a pair of N-channel MOSFETs for the bottom of the bridge and a pair of P-channel MOSFETs for the top diagonals of the bridge. The MOSFETs should be selected ...

Page 23

... REF input of the LTC2053 should be at least 1V below V DD dividing down the 2.5V reference with 500 of imped- ance, feeding this to the REF input of the LTC2053 and the integrating resistor of the LTC1923 error amplifier, any common mode issues will be avoided. 250 250 1 F ...

Page 24

... R DS(ON Two pairs of resistors, R ensure that the absolute maximum input voltage is not exceeded on the TEC voltage on TEC supply to the LTC1923 which, for this example, is 5V. The following equation will guarantee this where V BRIDGE circuitry and V These additional level shifting resistors affect some pa- rameters in the data sheet ...

Page 25

... PGND LTC1923 SS NDRVA I PDRVA LIM + V CS SET – FAULT THRM TEC + H/C TEC – V TEC TEC Figure 15. Higher Voltage Applications with the LTC1923 W U LTC1693-1 IN1 V CC1 GND1 OUT1 IN2 V CC2 4.7 F GND2 OUT2 0 0.1 F 4.7 F LTC1693-1 IN1 V CC1 GND1 OUT1 ...

Page 26

... LTC1923 U TYPICAL APPLICATIO 26 1923f ...

Page 27

... LTC DWG # 05-08-1641 0.229 – 0.244 (5.817 – 6.198 0.015 0.004 45 0.053 – 0.069 (0.38 0.10) (1.351 – 1.748) 0 – 8 TYP 0.008 – 0.012 (0.203 – 0.305) LTC1923 0.386 – 0.393* 0.033 (9.804 – 9.982) (0.838 1615 REF 0.150 – ...

Page 28

... LTC1923 PACKAGE DESCRIPTIO 5.35 0.05 4.20 0.05 3.45 0.05 (4 SIDES) RECOMMENDED SOLDER PAD LAYOUT 5.00 0.10 (4 SIDES) PIN 1 TOP MARK NOTE: 1. DRAWING PROPOSED TO INCLUDE JEDEC PACKAGE OUTLINE M0-220 VARIATION WHHD-(X) (TO BE APPROVED) 2. DRAWING NOT TO SCALE 3. ALL DIMENSIONS ARE IN MILLIMETERS 4. DIMENSIONS OF EXPOSED PAD ON BOTTOM OF PACKAGE DO NOT INCLUDE MOLD FLASH. MOLD FLASH, IF PRESENT, SHALL NOT EXCEED 0.20mm ON ANY SIDE 5 ...