ml6652 Sirenza Microdevices, ml6652 Datasheet

ml6652

Available stocks

Related parts for ml6652

ml6652 Summary of contents

Page 1

... Ethernet Fiber and Copper Media Converter with Auto-Negotiation GENERAL DESCRIPTION The ML6652 is a low cost multi-function / multi-standard single chip Media Converter that provides 10Mbps and 100Mbps signal conversion between twisted pair and fiber optic Ethernet technologies. The device supports conversion between: ...

Page 2

... Japan: 2,598,946; 2,619,299; 2,704,176; 2,821,714. Other patents are pending. 2 January 2004 Final Datasheet ML6652 DS6652-F-02 ...

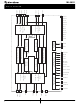

Page 3

... BLOCK DIAGRAM 3 January 2004 Final Datasheet ML6652 GNDB GNDQ VCCQ GNDFC VCCFC VCCL GNDL VCCD GNDD GNDE VCCE GNDT MDIO MDC DUPLEX SPEED AD10 AD32 AD4LIW PECLQU PECLTP TPOUTOFF# FOOUTOFF# PWRDWN# BCKLINK TPINSPD TPANDT FOINSPD FOANDT DS6652-F-02 ...

Page 4

... Note: this pin is typically read a few microseconds after power-up tied to supplies that do not track the ML6652 power improper results will occur. Use VCCD (pin 19) as the pull up point, do not add decoupling capacitors to this input pin (without thoroughly understanding your PCB layout dynamics the safest course is to make short connections and do not add decoupling capacitors to this input pin) ...

Page 5

... Management Interface. Note: this pin is typically read a few microseconds after power-up tied to supplies that do not track the ML6652 power improper results will occur. Use VCCD (pin 19) as the pull up point, do not add decoupling capacitors to this input pin (without thoroughly understanding your PCB layout dynamics the safest course is to make short connections and do not add decoupling capacitors to this input pin) ...

Page 6

... Note: this pin is typically read a few microseconds after power-up tied to supplies that do not track the ML6652 power improper results will occur. Use VCCD (pin 19) as the pull up point, do not add decoupling capacitors to this input pin (without thoroughly understanding your PCB layout dynamics the safest course is to make short connections and do not add decoupling capacitors to this input pin) ...

Page 7

... Description DUPLEX and SPEED can be used concurrently to set the power up mode of the ML6652 see Tables 4 and 6. For Mode details see the General Description section of this data sheet. This input can have one of three levels: VCC, VCC/2, and 0Volts. The input has 80kΩ resistors internally connected to both VCC and Ground generating VCC/2 at the input, if left unconnected ...

Page 8

... FLP Burst, or 10BASE-T signal from the network. The common mode voltage is set internally and the differential input resistance is about 2kΩ. The network termination must be added externally. It should contain a 100Ω resister between pin 10 and 11 as shown in Figure 1. January 2004 Final Datasheet ML6652 DS6652-F-02 ...

Page 9

... LED. The output data is NRZI encoded 100BASE-FX or 100BASE- SX symbols during 100Mbps mode, Manchester encoded 10BASE-FL data or OPT_IDL (10BASE-FL idle signal) during 10Mbps mode, and FLNP Bursts during Auto-Negotiation. IOUT# (pin 22) is optionally used to provide current peaking. If peaking is January 2004 Final Datasheet ML6652 ML6652 DS6652-F-02 ...

Page 10

... Optic Interface" mode. The two operating modes available for this pin are selected with the configuration pin PECLQU or the configuration bit PECLQU <30.7> Fiber Optic Interface Mode: This pin is not used and should be connected to VCC. January 2004 Final Datasheet ML6652 DS6652-F-02 ...

Page 11

... Note: This pin is typically read a few microseconds after power-up tied to supplies that do not track the ML6652 power, improper results may occur. For BCKPLINK, use VCCD (pin 19) as the pull up point, do not add decoupling ...

Page 12

... Power supply for CMOS noisy circuits. Power supply for the fiber optic LED driver output stage. Power supply for one PLL, part of the scrambler, fiber optic LED driver, and quantizer. Power supply for the quantizer and central bias. January 2004 Final Datasheet ML6652 DS6652-F-02 ...

Page 13

... Negotiation Pulses (FLNP). It supports ISO/IEC 8802.3, IEEE 802.3, and TIA/EIA-785 including Auto-Negotiation on both twisted pair and fiber optics. The ML6652 data interfaces can all be configured in a number of ways. The twisted pair inputs and outputs can be configured in Twisted Pair Mode to interface with a 1:1 transformer for transmit and receive or in PECL/LVPECL Mode to interface a PMD module ...

Page 14

... PWRDWN#. 14 SERIAL MANAGEMENT INTERFACE The ML6652 has management functions controlled by three sixteen bit registers and status updated by one sixteen bit registers. Management Data is input and output through MDIO and clocked by MDC in an interface compatible with the protocol defined in clause 22 of IEEE Std 802.3-1998 MII Serial Management Interface. The address bits PHYAD < ...

Page 15

... NON-TRANSPARENT are chosen at power up by setting of the DUPLEX and SPEED pins. Thereafter the operating modes may be set by toggling bits in management register 30. DUPLEX and SPEED must be used concurrently to set the mode of the ML6652 see Tables 6 and 7. Management Bit <30.11> Interface Operating TRANSPARENT# Modes ...

Page 16

... FO input and the DUPLEX mode selected through the DUPLEX pin or through the management interface bits 30.15 and 30.10 The ML6652 will transmit FLP Bursts as long as it receives FLP Bursts from the TP link partner. (The decision that the link is settled will be made by the TP link partner.) ...

Page 17

... SPEED input at VCC bits in management register 30. If the Fiber Optic Link Partner is Auto-Negotiation capable the ML6652 will allow the fiber optic link partner to Auto- Negotiate through the ML6652 to the twisted pair link partner. In this special case the non-transparent mode acts in the same way as the transparent mode ...

Page 18

... LED Status indicators are available: i) Pin 41 (TPINSPD) ii) Pin 42 (FOINSPD) iii) Pin 43 (TPANDT) iv) Pin 44 (FOANDT) Thus the ML6652 is designed to self-configure in stand alone applications as well as act under the control of a microprocessor or other control device in a managed setting. 18 TRANSPARENT MODE Twisted Pair Input/Output Interface ...

Page 19

... PWRDWN# the logic levels at configuration input pins DUPLEX (pin 25), SPEED (pin 27), PECLTP (pin 7), PECLQU (pin 8), AD4LIW (pin 4), and BCKLINK (Pin 40) are latched in the ML6652 and all management control register bits are reset. Enabled by setting management register bit <31.15> high, ...

Page 20

... Table Table 9. LED Colors vs. Resistor Values for Figure 4 January 2004 Final Datasheet ML6652 ...

Page 21

... Setting bit to 0 and TRANSPARENT# <30.11> set to 1 causes Full Duplex capability to be advertised in FLP bursts Setting bits to 1 and TRANSPARENT# <30.11> set to 0 causes Full Duplex capability to not be advertised in FLP bursts Setting TRANSPARENT# <30.11> causes ADVERFTD ignored 21 January 2004 Final Datasheet ML6652 R/W Default R/W 0 R/W 0 R/W 0 ...

Page 22

... Set high (1) disables Far-End-Fault pattern generation and detection. 1 BCKPDIS Set high (1) disables Backup Link function and overwrites BCKPLINK (40) configuration setting. 0 Reserved 22 1C (hex) All bits are Read Write January 2004 Final Datasheet ML6652 R/W Default R/W Set by SPEED (pin 27) R/W Set by SPEED (pin 27) ...

Page 23

... This bit set high when a data packet has been detected at the fiber optic input. This bit is latched high until it’s read. This bit is always low if both FOIN10 and FOIN100 are off 0 FLNP This bit set high when FLNP Bursts are detected at the fiber optic input interface 23 January 2004 Final Datasheet ML6652 DS6652-F-02 ...

Page 24

... Input Low Leakage Current 24 OPERATING CONDITIONS Power Supply Voltage Range ............................ 3.3V ±5% All VCC supply pins must be within 0.1V of each other Operating Temperature Range ......................................... ML6652CH/ML6652CM ............................... 0°C to 70°C ML6652EH/ML6652EM ............................ -20°C to 85°C CONDITIONS RTTP= 2KΩ RTOP=1.4KΩ Current into all VCC pins RTOP=1.4KΩ ...

Page 25

... With recommended resistor network. Refer to pin description With recommended resistor network. Refer to pin description With recommended resistor network. Refer to pin description With recommended resistor network. Refer to pin description January 2004 Final Datasheet ML6652 MIN TYP MAX UNITS 0.9 x VCCD VCCD V 0.4 x VCCD 0.6 x VCCD ...

Page 26

... RTOP = 1.4KΩ Fiber Optic Transmitter Turned Off 1.4V Crossing 1.4V Crossing 1.4V Crossing 1.4V Crossing 1.4V Crossing 1.4V Crossing 100Mbps 10Mbps 100Mbps 10Mbps 100Mbps 25MHz Nominal 10 to 90%, 5pF at each pin 100BASE-SX January 2004 Final Datasheet ML6652 MIN TYP MAX UNITS VCC-1.0 VCC-0.4 V 1.8 2.8 KΩ 110 330 µ ± ...

Page 27

... Low bandwidth, 10Mbps, Long Wave Length High bandwidth, 100Mbps, Short Wave Length High bandwidth, 100Mbps, Long Wave Length Short link distance (300m, High bandwidth path 100Mbps) 10Mbps or Auto-Negotiation 100Mbps 10BASE-FL 100BASE-SX 10BASE-FL 100BASE-SX January 2004 Final Datasheet ML6652 MIN TYP MAX UNITS 0.8 Vp-p 0.4 Vp-p 0.52 Vp 0.55 Vp ...

Page 28

... LPCC 33 EXPOSED PAD 7.00 ± .010 22 BOTTOM VIEW 0.90 ± 0.10 SEATING PLANE 0.20 REF. PACKAGE 44 Pin TQFP 44 Pin TQFP 44 Pin LPCC/QFN 44 Pin LPCC/QFN January 2004 Final Datasheet ML6652 inches (millimeters) 0.003 - 0.008 (0.09 - 0.20) 0.018 - 0.030 (0.45 - 0.75) SEATING PLANE 5.00 BSC 0.50 BSC 0.30-0.50 5.8 x 5.8 BSC 0.18-0.30 DATASHEET PUBLICATION DATE DS6652-F-02 ...