mpc9893 Integrated Device Technology, mpc9893 Datasheet

mpc9893

Available stocks

Related parts for mpc9893

mpc9893 Summary of contents

Page 1

... Ambient operating temperature range of -40 to 85°C Functional Description The MPC9893 2.5 V compatible PLL clock driver and clock generator. The clock generator uses a fully integrated PLL to generate clock signals from redundant clock sources. The PLL multiplies the input reference clock signal by one, two, three, four or eight. ...

Page 2

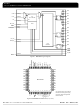

... MPC9893 Figure 2. MPC9893 48-Lead Pinout (Top View Data Generator D Q GND 24 23 QB0 QB1 GND 20 QB2 19 18 QB3 V ...

Page 3

... Please see the application CC_PLL 1 PLL bypassed and IDCS disabled. The VCO output is replaced by the reference clock signal fref. The MPC9893 is in manual mode. Automatic clock switch mode. IDCS enabled. Clock failure detection and output flags ALARM0, ALARM1, CLK_IND are enabled. IDCS overrides REF_SEL on a clock failure. ...

Page 4

... Unit ÷ 4.0 pF Max Unit ±20 mA ±50 mA °C 125 MPC9893 REV. 7 MARCH 3, 2008 (1) QFB REF f 8 REF f 6 REF f 8 REF f 4 REF f 16 REF f 8 REF f 4 REF Condition Per output Inputs ...

Page 5

... Maximum Quiescent Supply Current CC V Output Termination Voltage TT 1. The MPC9893 is capable of driving 50 Ω transmission lines on the incident edge. Each output drives one 50 Ω parallel terminated transmission line to a termination voltage of V output. IDT™ / ICS™ 3.3V 1:12 LVCMOS PLL CLOCK GENERATOR = 3.3 V ± 5 – ...

Page 6

... 225 ps See applications 425 ps section 150 ps See applications 250 ps section See applications 40 ps section 0.8-4.0 MHz 10 ms APPLICATIONS INFORMATION for more information MPC9893 REV. 7 MARCH 3, 2008 Condition ...

Page 7

... AC and DC specification for the input reference clock. A loss of clock is detected if as well as the loss of both clocks. In the case of both clocks lost, the MPC9893 will set the alarm flags and the PLL will stall. The MPC9893 does not monitor and detect changes in the input frequency ...

Page 8

... In the following example calculation jitter confidence factor of 99.7% (± 3σ) is assumed, resulting in a worst case timing uncertainty from the common clock input to any MPC9893 output of –275 ps to +265 ps relative to the reference clock input CLK0/1: t SK(PP) ...

Page 9

... MPC9893 3.3V 1:12 LVCMOS PLL CLOCK GENERATOR The I/O (Phase) jitter of the MPC9893 depends on the internal VCO frequency and the PLL feedback divider configuration. A high internal VCO frequency and a low PLL feedback divider result in lower I/O jitter than the jitter limits in the AC characteristics (Table 8). When calculating the part-to-part skew, ...

Page 10

... Figure 9 show the simulation results of an output driving a single line versus two lines. In both cases the drive capability of the MPC9893 output buffer is more than sufficient to drive 50 Ω transmission lines on the incident edge. Note from the delay measurements in the simulations a delta of only 43 ps exists between the two differently loaded outputs ...

Page 11

... Figure 15. I/O Jitter T JIT(PER The deviation in cycle time of a signal with respect to the ideal period over a random sample of cycles Figure 17. Period Jitter 2.4 1.8 0.55 0.6 MPC9893 V CC ÷ GND ÷ GND , static phase = |T –T mean mean in a random sample ...

Page 12

... G 0.500 BSC H 0.050 0.150 J 0.090 0.200 K 0.500 0.700 L 0˚ 7˚ M 12˚ REF N 0.090 0.160 P 0.250 BSC R 0.150 0.250 S 9.000 BSC S1 4.500 BSC V 9.000 BSC V1 4.500 BSC W 0.200 REF AA 1.000 REF R L˚ MPC9893 REV. 7 MARCH 3, 2008 ...

Page 13

... MPC9893 3.3V 1:12 LVCMOS PLL CLOCK GENERATOR Innovate with IDT and accelerate your future networks. Contact: www.IDT.com For Sales 800-345-7015 408-284-8200 Fax: 408-284-2775 Corporate Headquarters Integrated Device Technology, Inc. 6024 Silver Creek Valley Road San Jose, CA 95138 United States 800 345 7015 +408 284 8200 (outside U.S.) © ...