MC9S08AC16CFJE Freescale Semiconductor, MC9S08AC16CFJE Datasheet - Page 113

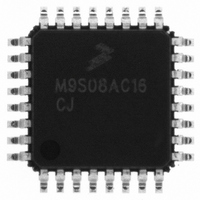

MC9S08AC16CFJE

Manufacturer Part Number

MC9S08AC16CFJE

Description

IC MCU 8BIT 16K FLASH 32-LQFP

Manufacturer

Freescale Semiconductor

Series

HCS08r

Specifications of MC9S08AC16CFJE

Core Processor

HCS08

Core Size

8-Bit

Speed

40MHz

Connectivity

I²C, SCI, SPI

Peripherals

LVD, POR, PWM, WDT

Number Of I /o

22

Program Memory Size

16KB (16K x 8)

Program Memory Type

FLASH

Ram Size

1K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 5.5 V

Data Converters

A/D 6x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

32-LQFP

Processor Series

S08AC

Core

HCS08

Data Bus Width

8 bit

Data Ram Size

1 KB

Interface Type

SCI/SPI

Maximum Clock Frequency

40 MHz

Number Of Programmable I/os

22

Number Of Timers

8

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

3rd Party Development Tools

EWS08

Development Tools By Supplier

DEMO9S08AC60E, DEMOACEX, DEMOACKIT, DCF51AC256, DC9S08AC128, DC9S08AC16, DC9S08AC60, DEMO51AC256KIT

Minimum Operating Temperature

- 40 C

On-chip Adc

6-ch x 10-bit

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MC9S08AC16CFJE

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

Company:

Part Number:

MC9S08AC16CFJER

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

- Current page: 113 of 336

- Download datasheet (7Mb)

7.4.1

Reset can be caused by a power-on-reset (POR) event, internal conditions such as the COP (computer

operating properly) watchdog, or by assertion of an external active-low reset pin. When a reset event

occurs, the CPU immediately stops whatever it is doing (the MCU does not wait for an instruction

boundary before responding to a reset event). For a more detailed discussion about how the MCU

recognizes resets and determines the source, refer to the

chapter.

The reset event is considered concluded when the sequence to determine whether the reset came from an

internal source is done and when the reset pin is no longer asserted. At the conclusion of a reset event, the

CPU performs a 6-cycle sequence to fetch the reset vector from 0xFFFE and 0xFFFF and to fill the

instruction queue in preparation for execution of the first program instruction.

7.4.2

When an interrupt is requested, the CPU completes the current instruction before responding to the

interrupt. At this point, the program counter is pointing at the start of the next instruction, which is where

the CPU should return after servicing the interrupt. The CPU responds to an interrupt by performing the

same sequence of operations as for a software interrupt (SWI) instruction, except the address used for the

vector fetch is determined by the highest priority interrupt that is pending when the interrupt sequence

started.

The CPU sequence for an interrupt is:

After the CCR contents are pushed onto the stack, the I bit in the CCR is set to prevent other interrupts

while in the interrupt service routine. Although it is possible to clear the I bit with an instruction in the

interrupt service routine, this would allow nesting of interrupts (which is not recommended because it

leads to programs that are difficult to debug and maintain).

For compatibility with the earlier M68HC05 MCUs, the high-order half of the H:X index register pair (H)

is not saved on the stack as part of the interrupt sequence. The user must use a PSHH instruction at the

beginning of the service routine to save H and then use a PULH instruction just before the RTI that ends

the interrupt service routine. It is not necessary to save H if you are certain that the interrupt service routine

does not use any instructions or auto-increment addressing modes that might change the value of H.

The software interrupt (SWI) instruction is like a hardware interrupt except that it is not masked by the

global I bit in the CCR and it is associated with an instruction opcode within the program so it is not

asynchronous to program execution.

Freescale Semiconductor

1. Store the contents of PCL, PCH, X, A, and CCR on the stack, in that order.

2. Set the I bit in the CCR.

3. Fetch the high-order half of the interrupt vector.

4. Fetch the low-order half of the interrupt vector.

5. Delay for one free bus cycle.

6. Fetch three bytes of program information starting at the address indicated by the interrupt vector

to fill the instruction queue in preparation for execution of the first instruction in the interrupt

service routine.

Reset Sequence

Interrupt Sequence

MC9S08AC16 Series Data Sheet, Rev. 8

Resets, Interrupts, and System Configuration

Chapter 7 Central Processor Unit (S08CPUV2)

113

Related parts for MC9S08AC16CFJE

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: