MC9S08AC16CFJE Freescale Semiconductor, MC9S08AC16CFJE Datasheet - Page 179

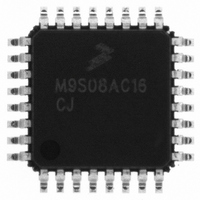

MC9S08AC16CFJE

Manufacturer Part Number

MC9S08AC16CFJE

Description

IC MCU 8BIT 16K FLASH 32-LQFP

Manufacturer

Freescale Semiconductor

Series

HCS08r

Specifications of MC9S08AC16CFJE

Core Processor

HCS08

Core Size

8-Bit

Speed

40MHz

Connectivity

I²C, SCI, SPI

Peripherals

LVD, POR, PWM, WDT

Number Of I /o

22

Program Memory Size

16KB (16K x 8)

Program Memory Type

FLASH

Ram Size

1K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 5.5 V

Data Converters

A/D 6x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

32-LQFP

Processor Series

S08AC

Core

HCS08

Data Bus Width

8 bit

Data Ram Size

1 KB

Interface Type

SCI/SPI

Maximum Clock Frequency

40 MHz

Number Of Programmable I/os

22

Number Of Timers

8

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

3rd Party Development Tools

EWS08

Development Tools By Supplier

DEMO9S08AC60E, DEMOACEX, DEMOACKIT, DCF51AC256, DC9S08AC128, DC9S08AC16, DC9S08AC60, DEMO51AC256KIT

Minimum Operating Temperature

- 40 C

On-chip Adc

6-ch x 10-bit

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MC9S08AC16CFJE

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

Company:

Part Number:

MC9S08AC16CFJER

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

- Current page: 179 of 336

- Download datasheet (7Mb)

to avoid such settings.) The TPM channel could still be used in output compare mode for software timing

functions (pin controls set not to affect the TPM channel pin).

10.6.1.2

An interrupt flag and enable are associated with the 16-bit main counter. The flag (TOF) is a

software-accessible indication that the timer counter has overflowed. The enable signal selects between

software polling (TOIE=0) where no hardware interrupt is generated, or interrupt-driven operation

(TOIE=1) where a static hardware interrupt is generated whenever the TOF flag is equal to one.

The conditions causing TOF to become set depend on whether the TPM is configured for center-aligned

PWM (CPWMS=1). In the simplest mode, there is no modulus limit and the TPM is not in CPWMS=1

mode. In this case, the 16-bit timer counter counts from 0x0000 through 0xFFFF and overflows to 0x0000

on the next counting clock. TOF becomes set at the transition from 0xFFFF to 0x0000. When a modulus

limit is set, TOF becomes set at the transition from the value set in the modulus register to 0x0000. When

the TPM is in center-aligned PWM mode (CPWMS=1), the TOF flag gets set as the counter changes

direction at the end of the count value set in the modulus register (that is, at the transition from the value

set in the modulus register to the next lower count value). This corresponds to the end of a PWM period

(the 0x0000 count value corresponds to the center of a period).

10.6.1.3

The main timer counter has two counting modes. When center-aligned PWM is selected (CPWMS=1), the

counter operates in up/down counting mode. Otherwise, the counter operates as a simple up counter. As

an up counter, the timer counter counts from 0x0000 through its terminal count and then continues with

0x0000. The terminal count is 0xFFFF or a modulus value in TPMxMODH:TPMxMODL.

When center-aligned PWM operation is specified, the counter counts up from 0x0000 through its terminal

count and then down to 0x0000 where it changes back to up counting. Both 0x0000 and the terminal count

value are normal length counts (one timer clock period long). In this mode, the timer overflow flag (TOF)

becomes set at the end of the terminal-count period (as the count changes to the next lower count value).

10.6.1.4

The main timer counter can be manually reset at any time by writing any value to either half of

TPMxCNTH or TPMxCNTL. Resetting the counter in this manner also resets the coherency mechanism

in case only half of the counter was read before resetting the count.

10.6.2

Provided CPWMS=0, the MSnB and MSnA control bits in the channel n status and control registers

determine the basic mode of operation for the corresponding channel. Choices include input capture,

output compare, and edge-aligned PWM.

Freescale Semiconductor

Channel Mode Selection

Counter Overflow and Modulo Reset

Counting Modes

Manual Counter Reset

MC9S08AC16 Series Data Sheet, Rev. 8

Timer/PWM Module (S08TPMV3)

179

Related parts for MC9S08AC16CFJE

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: