MPC562MZP56 Freescale Semiconductor, MPC562MZP56 Datasheet - Page 254

MPC562MZP56

Manufacturer Part Number

MPC562MZP56

Description

IC MPU 32BIT 56MHZ PPC 388-PBGA

Manufacturer

Freescale Semiconductor

Series

MPC5xxr

Datasheet

1.MPC561MZP56.pdf

(1420 pages)

Specifications of MPC562MZP56

Core Processor

PowerPC

Core Size

32-Bit

Speed

56MHz

Connectivity

CAN, EBI/EMI, SCI, SPI, UART/USART

Peripherals

POR, PWM, WDT

Number Of I /o

64

Program Memory Type

ROMless

Ram Size

32K x 8

Voltage - Supply (vcc/vdd)

2.5 V ~ 2.7 V

Data Converters

A/D 32x10b

Oscillator Type

External

Operating Temperature

-40°C ~ 125°C

Package / Case

388-BGA

Processor Series

MPC5xx

Core

PowerPC

Data Bus Width

32 bit

Data Ram Size

8 KB

Interface Type

SCI, SPI, UART

Maximum Clock Frequency

40 MHz

Number Of Programmable I/os

56

Number Of Timers

22

Operating Supply Voltage

2.6 V to 5 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Minimum Operating Temperature

- 40 C

On-chip Adc

2 (10 bit, 32 Channel)

For Use With

MPC564EVB - KIT EVAL FOR MPC561/562/563/564

Lead Free Status / RoHS Status

Request inventory verification / Request inventory verification

Eeprom Size

-

Program Memory Size

-

Lead Free Status / Rohs Status

No

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MPC562MZP56

Manufacturer:

FREESCAL

Quantity:

204

Company:

Part Number:

MPC562MZP56

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

Part Number:

MPC562MZP56

Manufacturer:

FREESCALE

Quantity:

20 000

Company:

Part Number:

MPC562MZP56R2

Manufacturer:

RFT

Quantity:

1 441

Company:

Part Number:

MPC562MZP56R2

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

- Current page: 254 of 1420

- Download datasheet (11Mb)

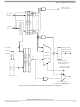

System Configuration and Protection

6.1.4.4.1

This feature (if enabled) simplifies the masking of lower priority interrupt requests when a request of

certain priority is in service in applications that require interrupt nesting. The highest (pending) request is

also masked by itself. The masking is accomplished in the following way.

Upon asserting an interrupt request the BBC generates an acknowledge signal to notify the interrupt

controller that the request and the branch table offset have been latched. The interrupt controller then sets

a bit in the SISR register (interrupt in-service register), according to the asserted request. All other requests

whose priority is lower than or equal to the one that is currently in-service, become masked. The mask

remains set until the SISR bit is cleared by software (by the interrupt handler routine), writing a ‘1’ value

to the corresponding bit. The lower priority request masking diagram is presented in

The lower priority request masking feature is disabled by HRESET and it may be enabled by setting the

LPMASK_EN bit in the SIUMCR register.

The feature must be activated only together with exception table relocation in the BBC module.

6.1.4.4.2

The enhanced interrupt controller is a feature that may be enabled according to a user’s application using

the EICEN control bit in SIUMCR register, which can be set and cleared at any time by software. If the bit

is cleared, the default interrupt controller operation is available, as described in

Interrupt Controller Operation (MPC555/MPC556-Compatible

compatible with the interrupt controller already implemented in MPC555/MPC556.

Figure 6-5

6-14

IMPU

acknowledge

Reset by

software

SIPEND [i]

SIMASK [i]

illustrates the interrupt controller functionality in the MPC561/MPC563.

Lower Priority Request Masking

In the regular mode of the interrupt controller the lower priority request

masking feature is not available.

Backward Compatibility with MPC555/MPC556

Figure 6-4. Lower Priority Request Masking—One Bit Diagram

MPC561/MPC563 Reference Manual, Rev. 1.2

Reset

Set

SISR[i]

From bit i - 1

NOTE

Enable

control bit

(LPMASK_EN)

To bit i + 1

Mode).” The regular operation is fully

Section 6.1.4.3, “Regular

To SIVEC

generation

Freescale Semiconductor

To RCPU

External

interrupt

request

generation

(OR between

all the bits)

Figure

6-4.

Related parts for MPC562MZP56

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Mpc562 32 Bit Powerpc Microcontroller

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

MPC5 1K0 5%

Manufacturer:

TE Connectivity

Datasheet:

Part Number:

Description:

MPC5 500R 5%

Manufacturer:

TE Connectivity

Datasheet:

Part Number:

Description:

MPC5 5K0 5%

Manufacturer:

Tyco Electronics

Datasheet:

Part Number:

Description:

MPC5 5R0 5%

Manufacturer:

Tyco Electronics

Datasheet:

Part Number:

Description:

MPC5 50K 5%

Manufacturer:

Tyco Electronics

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: