ATMEGA16-16MQ Atmel, ATMEGA16-16MQ Datasheet - Page 117

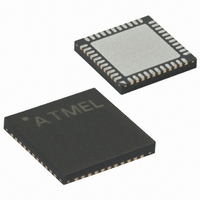

ATMEGA16-16MQ

Manufacturer Part Number

ATMEGA16-16MQ

Description

MCU AVR 16K FLASH 16MHZ 44-QFN

Manufacturer

Atmel

Series

AVR® ATmegar

Datasheet

1.ATMEGA16L-8MI.pdf

(357 pages)

Specifications of ATMEGA16-16MQ

Core Processor

AVR

Core Size

8-Bit

Speed

16MHz

Connectivity

I²C, SPI, UART/USART

Peripherals

Brown-out Detect/Reset, POR, PWM, WDT

Number Of I /o

32

Program Memory Size

16KB (8K x 16)

Program Memory Type

FLASH

Eeprom Size

512 x 8

Ram Size

1K x 8

Voltage - Supply (vcc/vdd)

4.5 V ~ 5.5 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

44-VQFN Exposed Pad

Processor Series

ATMEGA16x

Core

AVR8

Data Bus Width

8 bit

Data Ram Size

1 KB

Mounting Style

SMD/SMT

3rd Party Development Tools

EWAVR, EWAVR-BL

Development Tools By Supplier

ATAVRDRAGON, ATSTK500, ATSTK600, ATAVRISP2, ATAVRONEKIT

For Use With

ATSTK600-TQFP44 - STK600 SOCKET/ADAPTER 44-TQFPATSTK500 - PROGRAMMER AVR STARTER KIT

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

- Current page: 117 of 357

- Download datasheet (8Mb)

8-bit

Timer/Counter2

with PWM and

Asynchronous

Operation

Overview

Registers

2466T–AVR–07/10

Timer/Counter2 is a general purpose, single compare unit, 8-bit Timer/Counter module. The

main features are:

•

•

•

•

•

•

•

A simplified block diagram of the 8-bit Timer/Counter is shown in

ment of I/O pins, refer to

I/O bits and I/O pins, are shown in bold. The device-specific I/O Register and bit locations are

listed in the

Figure 53. 8-bit Timer/Counter Block Diagram

The Timer/Counter (TCNT2) and Output Compare Register (OCR2) are 8-bit registers. Interrupt

request (shorten as Int.Req.) signals are all visible in the Timer Interrupt Flag Register (TIFR).

All interrupts are individually masked with the Timer Interrupt Mask Register (TIMSK). TIFR and

TIMSK are not shown in the figure since these registers are shared by other timer units.

The Timer/Counter can be clocked internally, via the prescaler, or asynchronously clocked from

the TOSC1/2 pins, as detailed later in this section. The asynchronous operation is controlled by

the Asynchronous Status Register (ASSR). The Clock Select logic block controls which clock

source the Timer/Counter uses to increment (or decrement) its value. The Timer/Counter is inac-

tive when no clock source is selected. The output from the Clock Select logic is referred to as the

timer clock (clk

Single Compare unit Counter

Clear Timer on Compare Match (Auto Reload)

Glitch-free, Phase Correct Pulse Width Modulator (PWM)

Frequency Generator

10-bit Clock Prescaler

Overflow and Compare Match Interrupt Sources (TOV2 and OCF2)

Allows clocking from External 32 kHz Watch Crystal Independent of the I/O Clock

Status flags

“8-bit Timer/Counter Register Description” on page

T2

Timer/Counter

).

TCNTn

OCRn

=

“Pinout ATmega16” on page

ASSRn

direction

count

clear

BOTTOM

Synchronized Status flags

= 0

Control Logic

=

TCCRn

TOP

asynchronous mode

0xFF

select (ASn)

clk

2. CPU accessible I/O Registers, including

Tn

Synchronization Unit

OCn

(Int.Req.)

Generation

Prescaler

Waveform

128.

Figure

ATmega16(L)

53. For the actual place-

Oscillator

T/C

clk

TOVn

(Int.Req.)

clk

clk

OCn

ASY

I/O

I/O

TOSC1

TOSC2

117

Related parts for ATMEGA16-16MQ

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Atmel Corporation

Datasheet:

Part Number:

Description:

IC AVR MCU 16K 16MHZ 5V 44TQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC AVR MCU 16K 16MHZ 5V 44-QFN

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC AVR MCU 16K 16MHZ 5V 40DIP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC AVR MCU 16K 16MHZ COM 40-DIP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC AVR MCU 16K 16MHZ COM 44-QFN

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC AVR MCU 16K 16MHZ IND 40-DIP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC AVR MCU 16K 16MHZ IND 44-QFN

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC AVR MCU 16K 16MHZ IND 44-TQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC MCU 8BIT 16KB FLASH 44TQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU AVR 16K FLASH 16MHZ 44-TQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC AVR MCU 16K 16MHZ COM 44-TQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC MCU AVR 16K 5V 16MHZ 44-TQFP

Manufacturer:

Atmel

Datasheet: