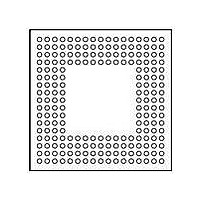

LPC3152FET208,551 NXP Semiconductors, LPC3152FET208,551 Datasheet - Page 24

LPC3152FET208,551

Manufacturer Part Number

LPC3152FET208,551

Description

IC ARM9 MCU USB OTG 208TFBGA

Manufacturer

NXP Semiconductors

Series

LPC3000r

Datasheet

1.EA-OEM-306.pdf

(88 pages)

Specifications of LPC3152FET208,551

Package / Case

208-TFBGA

Core Processor

ARM9

Core Size

32-Bit

Speed

180MHz

Connectivity

EBI/EMI, I²C, IrDA, MMC, PCM, SPI, UART/USART, USB OTG

Peripherals

DMA, I²S, LCD, PWM, WDT

Number Of I /o

10

Program Memory Type

ROMless

Ram Size

192K x 8

Voltage - Supply (vcc/vdd)

1.1 V ~ 3.6 V

Data Converters

A/D 3x10b

Oscillator Type

External

Operating Temperature

-40°C ~ 85°C

Processor Series

LPC31

Core

ARM926EJS

Data Bus Width

32 bit

Data Ram Size

192 KB

Interface Type

I2C, I2S, SPI, UART

Maximum Clock Frequency

180 MHz

Number Of Timers

5

Operating Supply Voltage

1.2 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

3rd Party Development Tools

MDK-ARM, RL-ARM, ULINK2

Development Tools By Supplier

OM11029

Minimum Operating Temperature

- 40 C

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Program Memory Size

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Other names

935287561551

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

LPC3152FET208,551

Manufacturer:

NXP Semiconductors

Quantity:

10 000

NXP Semiconductors

LPC3152_3154

Preliminary data sheet

6.12 Interrupt controller

6.13 Multi-layer AHB

The interrupt controller collects interrupt requests from multiple devices, masks interrupt

requests, and forwards the combined requests to the processor. The interrupt controller

also provides facilities to identify the interrupt requesting devices to be served.

This module has the following features:

The following blocks can generate interrupts:

The multi-layer AHB is an interconnection scheme, based on the AHB protocol that

enables parallel access paths between multiple masters and slaves in a system.

Multiple masters can have access to different slaves at the same time.

Figure 5

AHB masters and slaves are numbered according to their AHB port number.

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

The interrupt controller decodes all the interrupt requests issued by the on-chip

peripherals.

Two interrupt lines (Fast Interrupt Request (FIQ) and Interrupt Request (IRQ)) to the

ARM core. The ARM core supports two distinct levels of priority on all interrupt

sources, FIQ for high priority interrupts and IRQ for normal priority interrupts.

Software interrupt request capability associated with each request input.

Visibility of interrupts request state before masking.

Support for nesting of interrupt service routines.

Interrupts routed to IRQ and to FIQ are vectored.

Level interrupt support.

NAND flash controller

USB 2.0 HS OTG

Event router

10 bit ADC

UART

LCD int

MCI

SPI

Timer 0, timer 1, timer 2, and timer 3

I

I

DMA

I

2

2

2

S transmit: I2STX_0 and I2STX_1

S receive: I2SRX_0 and I2SRX_1

C0-bus and I

gives an overview of the multi-layer AHB configuration in the LPC3152/3154.

All information provided in this document is subject to legal disclaimers.

2

C1-bus

Rev. 0.12 — 27 May 2010

LPC3152/3154

© NXP B.V. 2010. All rights reserved.

24 of 88