P80C592FFA/00,512 NXP Semiconductors, P80C592FFA/00,512 Datasheet - Page 54

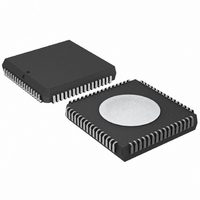

P80C592FFA/00,512

Manufacturer Part Number

P80C592FFA/00,512

Description

IC 80C51 MCU 8BIT ROMLESS 68PLCC

Manufacturer

NXP Semiconductors

Series

80Cr

Datasheet

1.P80C592FFA00512.pdf

(108 pages)

Specifications of P80C592FFA/00,512

Program Memory Type

ROMless

Package / Case

68-PLCC

Core Processor

8051

Core Size

8-Bit

Speed

16MHz

Connectivity

CAN, EBI/EMI, UART/USART

Peripherals

DMA, POR, PWM, WDT

Number Of I /o

48

Ram Size

512 x 8

Voltage - Supply (vcc/vdd)

4.5 V ~ 5.5 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Processor Series

P80C5x

Core

80C51

Data Bus Width

8 bit

Data Ram Size

512 B

Interface Type

CAN/UART

Maximum Clock Frequency

16 MHz

Number Of Programmable I/os

40

Number Of Timers

3

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

3rd Party Development Tools

PK51, CA51, A51, ULINK2

Minimum Operating Temperature

- 40 C

On-chip Adc

8-ch x 10-bit

Cpu Family

80C

Device Core

80C51

Device Core Size

8b

Frequency (max)

16MHz

Program Memory Size

Not Required

Total Internal Ram Size

512Byte

# I/os (max)

40

Number Of Timers - General Purpose

3

Operating Supply Voltage (typ)

5V

Operating Supply Voltage (max)

5.5V

Operating Supply Voltage (min)

4.5V

Instruction Set Architecture

CISC

Operating Temp Range

-40C to 85C

Operating Temperature Classification

Industrial

Mounting

Surface Mount

Pin Count

68

Package Type

PLCC

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Program Memory Size

-

Lead Free Status / Rohs Status

Compliant

Other names

568-1241-5

935086530512

P80C592FFAA

935086530512

P80C592FFAA

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

P80C592FFA/00,512

Manufacturer:

ON

Quantity:

300

Company:

Part Number:

P80C592FFA/00,512

Manufacturer:

NXP Semiconductors

Quantity:

10 000

Philips Semiconductors

13.5.20.1 Synchronization Rules

The synchronization rules are as follows:

13.6

13.6.1

The P8xC592's CAN-controller supports the four different

CAN-protocol frame types for communication:

13.6.1.1

There are two logical bit representations used in the

CAN-protocol:

1996 Jun 27

Only one synchronization within one bit time is used.

An edge is used for synchronization only if the value

detected at the previous sample point differs from the

bus value immediately after the edge.

Hard synchronization is performed whenever there is a

recessive-to-dominant edge during Bus-Idle

(see Section 13.6.6).

All other edges (recessive-to-dominant and optionally

dominant-to recessive edges if the Sync bit is set HIGH

(see Section 13.5.3) which are candidates for

resynchronization will be used with the following

exception:

– A transmitting CAN-controller will not perform a

Data Frame, to transfer data

Remote Frame, request for data

Error Frame, globally signal a (locally) detected error

condition

Overload Frame, to extend delay time of subsequent

frames (an Overload Frame is not initiated by the

P8xC592 CAN-controller).

A recessive bit on the bus-line appears only if all

connected CAN-controllers send a recessive bit at that

moment.

Dominant bits always overwrite recessive bits i.e. the

resulting bit level on the bus-line is dominant.

8-bit microcontroller with on-chip CAN

resynchronization as a result of a

recessive-to-dominant edge with positive phase

error, if only these edges are used for

resynchronization. This ensures that the delay times

of the output driver and input comparator do not

cause a permanent increase in the bit time.

CAN 2.0A Protocol description

F

RAME TYPES

Bit representation

54

13.6.2

A Data Frame carries data from a transmitting

CAN-controller to one or more receiving ones.

A Data Frame is composed of seven different bit-fields:

13.6.2.1

Signals the start of a Data Frame or Remote Frame.

It consists of a single dominant bit use for hard

synchronization of a CAN-controller in receive mode.

13.6.2.2

Consists of the message Identifier and the RTR bit. In the

case of simultaneous message transmissions by two or

more CAN-controllers the bus access conflict is solved by

bit-wise arbitration, which is active during the transmission

of the Arbitration Field.

13.6.2.3

This 11-bit field is used to provide information about the

message, as well as the bus access priority. It is

transmitted in the order ID.10 to ID.0 (LSB). The situation

that the seven most significant bits (ID.10 to ID.4) are all

recessive must not occur.

An Identifier does not define which particular

CAN-controller will receive the frame because a CAN

based communication network does not differentiate

between a point-to-point, multicast or broadcast

communication.

Start-Of-Frame

Arbitration Field

Control Field

Data Field (may have a length of zero)

CRC Field (CRC = Cyclic Redundancy Code)

Acknowledge Field

End-Of-Frame.

D

ATA

Start-Of-Frame bit

Arbitration Field

Identifier

F

RAME

Product specification

P8xC592