TMP86FS28DFG(JZ) Toshiba, TMP86FS28DFG(JZ) Datasheet - Page 93

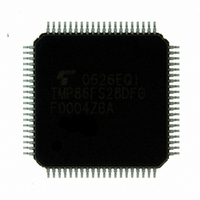

TMP86FS28DFG(JZ)

Manufacturer Part Number

TMP86FS28DFG(JZ)

Description

IC MCU 8BIT FLASH 60KB 80-LQFP

Manufacturer

Toshiba

Series

TLCS-870/Cr

Datasheet

1.TMP86FS28DFGJZ.pdf

(272 pages)

Specifications of TMP86FS28DFG(JZ)

Core Processor

870/C

Core Size

8-Bit

Speed

16MHz

Connectivity

SIO, UART/USART

Peripherals

LCD, PWM, WDT

Number Of I /o

62

Program Memory Size

60KB (60K x 8)

Program Memory Type

FLASH

Ram Size

2K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 5.5 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

80-LQFP

Processor Series

TLCS-870

Core

870/C

Data Bus Width

8 bit

Data Ram Size

2 KB

Interface Type

SIO, UART

Maximum Clock Frequency

16 MHz

Number Of Programmable I/os

62

Number Of Timers

6

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Development Tools By Supplier

BM1040R0A, BMP86A100010A, BMP86A100010B, BMP86A200010B, BMP86A200020A, BMP86A300010A, BMP86A300020A, BMP86A300030A, SW89CN0-ZCC, SW00MN0-ZCC

Minimum Operating Temperature

- 40 C

On-chip Adc

10 bit, 8 Channel

For Use With

BM1401W0A-G - FLASH WRITER ON-BOARD PROGRAMTMP89C900XBG - EMULATION CHIP TMP89F LQFP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Details

Other names

TMP86FS28DFGJZ

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

- Current page: 93 of 272

- Download datasheet (3Mb)

7.2 Divider Output (

7.2.1 Configuration

7.2.2 Control

Time Base Timer Control Register

buzzer drive. Divider output is from

Data output

Approximately 50% duty pulse can be output using the divider output circuit, which is useful for piezoelectric

Note: Selection of divider output frequency (DVOCK) must be made while divider output is disabled (DVOEN="0"). Also, in other

(0036H)

TBTCR

fc/2

fc/2

fc/2

fc/2

13

12

11

10

The Divider Output is controlled by the Time Base Timer Control Register.

words, when changing the state of the divider output frequency from enabled (DVOEN="1") to disable(DVOEN="0"), do not

change the setting of the divider output frequency.

or fs/2

or fs/2

or fs/2

or fs/2

5

4

3

2

Divider output control register

DVOCK

DVOEN

(a) configuration

DVOEN

DVOCK

7

Output latch

A

B

C

D

D

MPX

2

S

Y

TBTCR

Q

6

DVO

Divider output

enable / disable

Divider Output (

frequency selection: [Hz]

DVOCK

DVOEN

)

5

DVO

Figure 7-3 Divider Output

DVO

(DV7CK)

)

pin.

4

(TBTEN)

Page 81

DVO pin

0: Disable

1: Enable

3

00

01

10

11

Port output latch

TBTCR<DVOEN>

DVO pin output

DV7CK = 0

2

NORMAL1/2, IDLE1/2 Mode

fc/2

fc/2

fc/2

fc/2

13

12

10

11

(TBTCK)

1

(b) Timing chart

DV7CK = 1

0

fs/2

fs/2

fs/2

fs/2

5

4

3

2

(Initial value: 0000 0000)

SLEEP1/2

SLOW1/2

TMP86FS28DFG

Mode

fs/2

fs/2

fs/2

fs/2

5

4

3

2

R/W

R/W

Related parts for TMP86FS28DFG(JZ)

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Toshiba Semiconductor [TOSHIBA IGBT Module Silicon N Channel IGBT]

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA GTR MODULE SILICON NPN TRIPLE DIFFUSED TYPE

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA GTR Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA Intelligent Power Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA INTELLIGENT POWER MODULE SILICON N CHANNEL LGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA IGBT Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA GTR MODULE SILICON N−CHANNEL IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA Intelligent Power Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA GTR Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA INTELLIGENT POWER MODULE

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA Intelligent Power Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA Intelligent Power Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA IGBT Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA Intelligent Power Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

Toshiba Semiconductor [SILICON N CHANNEL 1GBT]

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet: