MPC564MZP66 Freescale Semiconductor, MPC564MZP66 Datasheet - Page 260

MPC564MZP66

Manufacturer Part Number

MPC564MZP66

Description

IC MCU 512K FLASH 66MHZ 388-BGA

Manufacturer

Freescale Semiconductor

Series

MPC5xxr

Specifications of MPC564MZP66

Core Processor

PowerPC

Core Size

32-Bit

Speed

66MHz

Connectivity

CAN, EBI/EMI, SCI, SPI, UART/USART

Peripherals

POR, PWM, WDT

Number Of I /o

56

Program Memory Size

512KB (512K x 8)

Program Memory Type

FLASH

Ram Size

32K x 8

Voltage - Supply (vcc/vdd)

2.5 V ~ 2.7 V

Data Converters

A/D 32x10b

Oscillator Type

External

Operating Temperature

-40°C ~ 125°C

Package / Case

388-BGA

For Use With

MPC564EVB - KIT EVAL FOR MPC561/562/563/564

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MPC564MZP66

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

Company:

Part Number:

MPC564MZP66R2

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

- Current page: 260 of 1420

- Download datasheet (11Mb)

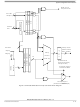

System Configuration and Protection

is not affected by reset and operates in all low-power modes. It is initialized by software. The RTC can be

programmed to generate a maskable interrupt when the time value matches the value programmed in its

associated alarm register. It can also be programmed to generate an interrupt once a second. A control and

status register is used to enable or disable the different functions and to report the interrupt source.

6.1.9

The periodic interrupt timer consists of a 16-bit counter clocked by the PITRTCLK clock signal supplied

by the clock module as shown in

The 16-bit counter counts down to zero when loaded with a value from the PITC register. After the timer

reaches zero, the PS bit is set and an interrupt is generated if the PIE bit is a logic one. The software service

routine should read the PS bit and then write a zero to terminate the interrupt request. At the next input

clock edge, the value in the PITC is loaded into the counter, and the process starts over again.

When a new value is written into the PITC, the periodic timer is updated, the divider is reset, and the

counter begins counting. If the PS bit is not cleared, an interrupt request is generated. The request remains

pending until PS is cleared. If the PS bit is set again prior to being cleared, the interrupt remains pending

until PS is cleared.

Any write to the PITC stops the current countdown, and the count resumes with the new value in PITC. If

the PISCR[PTE] bit is not set, the PIT is unable to count and retains the old count value. Reads of the PIT

have no effect on the counter value.

6-20

PITRTCLK

Clock

Periodic Interrupt Timer (PIT)

PITRTCLK can be divided by 4 or 256. See

Disable

FREEZE

Clock

MPC561/MPC563 Reference Manual, Rev. 1.2

Figure

Figure 6-7. RTC Block Diagram

By 15625

By 78125

RTSEC

6-8.

Divide

Divide

4-MHz/20-MHz crystal

NOTE

MUX

Table 8-1

32-bit Register (RTCAL)

32-bit Counter (RTC)

for default settings.

=

Freescale Semiconductor

Interrupt

Interrupt

Alarm

Sec

Related parts for MPC564MZP66

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

MPC5 1K0 5%

Manufacturer:

TE Connectivity

Datasheet:

Part Number:

Description:

MPC5 500R 5%

Manufacturer:

TE Connectivity

Datasheet:

Part Number:

Description:

MPC5 5K0 5%

Manufacturer:

Tyco Electronics

Datasheet:

Part Number:

Description:

MPC5 5R0 5%

Manufacturer:

Tyco Electronics

Datasheet:

Part Number:

Description:

MPC5 50K 5%

Manufacturer:

Tyco Electronics

Datasheet:

Part Number:

Description:

MPC5 1R0 5%

Manufacturer:

Tyco Electronics

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: