CS8371ETVA7 ON Semiconductor, CS8371ETVA7 Datasheet

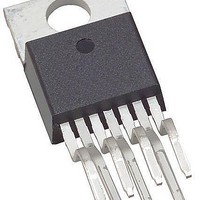

CS8371ETVA7

Specifications of CS8371ETVA7

Related parts for CS8371ETVA7

CS8371ETVA7 Summary of contents

Page 1

... Work Week G = Pb−Free Package ORDERING INFORMATION Device Package CS8371ET7 TO−220 STRAIGHT CS8371ET7G TO−220 STRAIGHT (Pb−Free) CS8371ETVA7 TO−220 VERTICAL CS8371ETVA7G TO−220 VERTICAL (Pb−Free) 1 TO−220 SEVEN LEAD T SUFFIX CASE 821E TO−220 SEVEN LEAD TVA SUFFIX CASE 821J Tab = GND Pin 1. ENABLE 1 2 ...

Page 2

V CC ENABLE − 1.2 V ENABLE − 1.2 V GND MAXIMUM RATINGS Power Dissipation ENABLE Input Voltage Range Load Current (8.0 V Regulator) Load Current (5.0 V Regulator) Transient Peak Voltage (31 V Load Dump ...

Page 3

ELECTRICAL CHARACTERISTICS 5.0 mA, unless otherwise stated.) OUT1 OUT2 Characteristic PRIMARY OUTPUT (V ) OUT1 Output Voltage I OUT1 10.5 V ≤ V Line Regulation 5.0 mA ≤ I Load Regulation Sleep Mode Quiescent Current V ...

Page 4

PACKAGE PIN DESCRIPTION PACKAGE LEAD # 7 Lead TO−220 TYPICAL PERFORMANCE CHARACTERISTICS 8. 8. 1.0 A OUT 8.03 8.02 8.01 8.00 7.99 7.98 7.97 7.96 7.95 ...

Page 5

TYPICAL PERFORMANCE CHARACTERISTICS 25° Reg 1 Output Current (A) Figure 6. Regulator 1 Current Limit 9.0 Enable 1 ...

Page 6

TYPICAL PERFORMANCE CHARACTERISTICS 8.020 8.015 8.010 8.005 −40°C 8.000 25°C 7.995 7.990 7.985 7.980 0 100 200 300 400 500 600 700 800 900 1000 Output Current (mA) Figure 12. Regulator 1 Load Regulation = ...

Page 7

TYPICAL PERFORMANCE CHARACTERISTICS OUT 25° −1 −2 −3 1000 Time (ms) Figure 18. Regulator 1 Load Transient Response 100 ...

Page 8

... ESR (Equivalent Series Resistance) and board layout parasitics all can create oscillations if not properly accounted for. NOCAP Semiconductor exclusive output stage which internally compensates the LDO regulator over temperature, load and line variations without the need for an expensive external capacitor. It incorporates high gain (> ...

Page 9

This will depend on the load conditions. With these types of loads, a traditional output stage may be better suited for proper operation. Output 1 employs NOCAP. Refer to the plots in the ...

Page 10

OPTIONAL CHAMFER SEATING PLANE −Q− 0.356 (0.014 CS8371 PACKAGE DIMENSIONS 7 LEAD, TO−220 T SUFFIX CASE 821E−04 ISSUE ...

Page 11

... Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner. PUBLICATION ORDERING INFORMATION LITERATURE FULFILLMENT: Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303−675−2175 or 800−344−3860 Toll Free USA/Canada Fax: 303− ...